Wetenschap

Samsung spreekt op gieterij-evenement over 3nm, MBCFET-ontwikkelingen

Krediet:Samsung

"Het nanometerproces houdt zich bezig met de ruimte tussen de transistors die op nanometerniveau op een substraat zijn gemonteerd, " zei Puls .

"Hoe kleiner de afstand, hoe meer chips erin kunnen worden geperst om de rekenkracht en energie-efficiëntie te vergroten. Een nanometer komt overeen met een tienduizendste van de diameter van een mensenhaar."

Op het Samsung Foundry Forum in Santa Clara, Californië, het bedrijf probeerde onlangs indruk te maken op de vooruitgang die het heeft geboekt in de 3nm gate-all-around (GAA) procesontwikkeling.

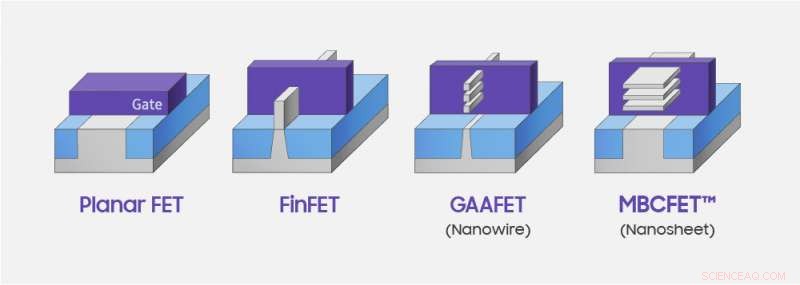

Samsung Foundry introduceert nu MBCFET (multi bridge channel FET). Deze bestaat uit multi-stacked nanosheets. Met de vorming van nanobladen, een grotere stroom per stapel is haalbaar, zei SamMobile .

ExtremeTech beschreef de aankondiging als gaand over "een nieuwe, geëvolueerde transistorarchitectuur" die uit Samsung Foundry komt - met de "nanosheets" -benadering voor zijn 3nm-knooppunt.

(Van de redactie van Samsung:"Conventionele GAA op basis van nanodraad vereist een groter aantal stapels vanwege de kleine effectieve kanaalbreedte. Aan de andere kant, Samsung's gepatenteerde versie van GAA, MBCFET (Multi-Bridge-Channel FET), maakt gebruik van een nanosheet-architectuur, waardoor een grotere stroom per stapel mogelijk is.")

De blog CNXSoft werpt verder licht op waarom de overgang van nanodraden naar nanosheets.

"We lezen vaak dat nieuwe processors worden vervaardigd met een FinFET-proces. Het nieuwe proces is ontstaan vanwege korte kanaaleffecten in traditionele planaire transistors, en FinFET (Fin Field-effect transistor) werd geïntroduceerd om verdere spanningsschaling mogelijk te maken, maar waarbij het procesknooppunt steeds kleiner wordt, elektrostatische effecten begonnen problemen te veroorzaken."

Het gebruik van GAA (Gate All Around) nanodraden om die effecten te beperken, werd als antwoord genomen, maar die zijn blijkbaar heel moeilijk te integreren in silicium, zei de blog, dus Samsung gebruikte uiteindelijk dunne lagen (nanosheets) in plaats van nanodraden, "het mogelijk maken van een grotere stroom per track in hun GAA-implementatie genaamd MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

Voor degenen die de overdaad aan acroniemen moeten verwerken, Ramish Zafar in Wccftech nam zijn lezers mee op de Samsung-reis. 1. Samsung werkte samen met IBM voor GAAFET (Gate-All-Around) procesknooppunten. 2. Nu heeft het bedrijf zijn aanpassingen aan het eerdere proces aangekondigd, en dit is MBCFET.

Zafar had meer te zeggen over MBCET. "In tegenstelling tot traditionele FinFET-ontwerpen, Met GAAFET kan het poortmateriaal het kanaal van alle kanten omringen. Samsung beweert dat het ontwerp van MBCFET het aan-uit-gedrag van het proces zal verbeteren, en processors in staat te stellen de bedrijfsspanning tot onder 0,75 V te verlagen. Een cruciaal punt voor MBCFET is dat het proces volledig compatibel is met FinFET-ontwerpen en geen nieuwe productietools vereist."

Krediet:Samsung

Hoe, Hoewel, speelt al dit goede nieuws een rol in de ontwikkelingsplannen van het bedrijf. Wanneer kunnen we technologie in actie verwachten? Joel Hruska behandelde dit in ExtremeTech .

"Op het Samsung Foundry Forum deze week, Samsung verklaarde dat zijn Product Design Kit voor 3nm-chips nu in alfa is, de 0,1 ontwikkelingsmijlpaal hebben bereikt. Samsung is van plan de komende jaren een overvloed aan procesknooppunten te lanceren, met ontwikkelingssporen gepland voor 7nm, 6nm, 5nm, 4nm, en ja, 3nm."

Hruska heeft toegevoegd, "De verbeteringen voor 3nm ten opzichte van 7nm zijn redelijk goed, maar dit knooppunt zal eigenlijk geruime tijd niet worden verzonden." Zijn artikel bevat een grafiek die de voortgang laat zien zoals gecommuniceerd door Samsung.

© 2019 Wetenschap X Netwerk

Hoofdlijnen

- Antibiotica ontdekking in de afgrond

- EU-handelsverbod verlaagt wereldhandel in wilde vogels met 90 procent

- De voordelen van het bestuderen van cellen onder een lichtmicroscoop

- Welke organellen bevinden zich in een prokaryote cel?

- Rollende dobbelstenen voor specificatie van celgrootte in epidermis van planten

- In bijensterfte, fungiciden komen naar voren als onwaarschijnlijke schurk

- Onderzoekers ontdekken dat stress tijdens de zwangerschap de grootte van de baby beïnvloedt

- Feiten over lipiden

- Vermindering van individuele plantengroei verhoogt soms de veerkracht van de gemeenschap

- Sensorische huid helpt zachte robots om zich te oriënteren

- Grote spelers springen in de stroom, Netflix-dominantie testen

- Eerste robotsysteem speelt Tic Tac Toe om de taakprestaties te verbeteren

- ShapeBots:een zwerm van vormveranderende robots die gegevens visueel weergeven

- Ongeliefde Airbus A380's worden gestript voor onderdelen

Onderzoekers observeren een uniek chiraal magnetisch fenomeen

Onderzoekers observeren een uniek chiraal magnetisch fenomeen Hoe lang duurt het voorschoolse voordeel?

Hoe lang duurt het voorschoolse voordeel? Directe kosten terugroeping Daimler-diesel in Europa beperkt

Directe kosten terugroeping Daimler-diesel in Europa beperkt DNA-apparaten voeren bio-analytische chemie uit in levende cellen

DNA-apparaten voeren bio-analytische chemie uit in levende cellen Laten we echt praten met universiteitsatleten over hun kansen om prof te worden

Laten we echt praten met universiteitsatleten over hun kansen om prof te worden Studie onthult de atmosferische voetafdruk van de onderbreking van de opwarming van de aarde

Studie onthult de atmosferische voetafdruk van de onderbreking van de opwarming van de aarde Ik ben een astronoom en ik denk dat er buitenaardse wezens zijn, maar UFO-waarnemingen zijn niet overtuigend

Ik ben een astronoom en ik denk dat er buitenaardse wezens zijn, maar UFO-waarnemingen zijn niet overtuigend Wat zijn de 10 meest voorkomende vormen van marteling en waarom?

Wat zijn de 10 meest voorkomende vormen van marteling en waarom?

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Swedish | Dutch | Danish | Norway | Portuguese | German |

-

Wetenschap © https://nl.scienceaq.com