Wetenschap

Powering the future:kleinste volledig digitale circuit opent deuren naar 5 nm next-gen halfgeleider

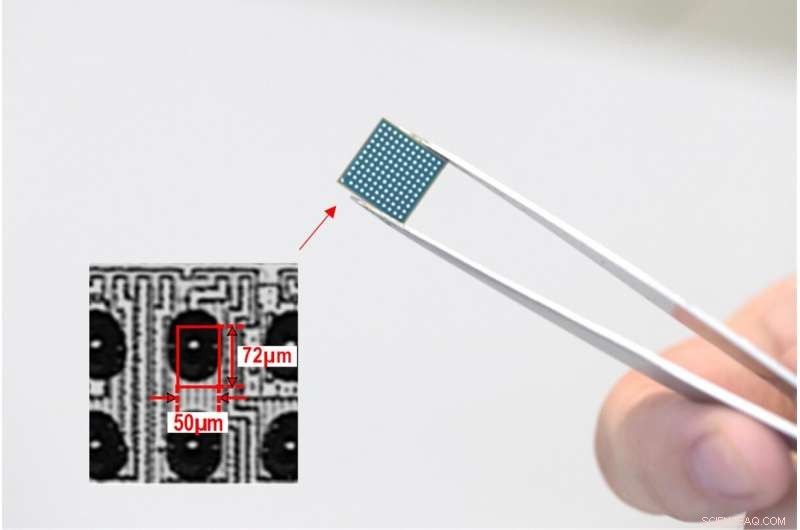

De volledige volledig digitale PLL past in een gebied van 50 × 72 μm2, waardoor het de kleinste PLL tot nu toe is. Krediet:Kenichi Okada

Wetenschappers van het Tokyo Institute of Technology (Tokyo Tech) en Socionext Inc. hebben 's werelds kleinste volledig digitale phase-locked loop (PLL) ontworpen. PLL's zijn kritieke klokcircuits in vrijwel alle digitale toepassingen, en het verkleinen van hun omvang en het verbeteren van hun prestaties is een noodzakelijke stap om de ontwikkeling van technologieën van de volgende generatie mogelijk te maken.

Nieuwe of verbeterde technologieën, zoals kunstmatige intelligentie, 5G mobiele communicatie, en het internet der dingen, wordt verwacht dat ze revolutionaire veranderingen in de samenleving teweeg zullen brengen. Maar om dat te laten gebeuren, high-performance system-on-a-chip (SoC) - een soort geïntegreerde schakeling - apparaten zijn onmisbaar. Een kernbouwsteen van SoC-apparaten is de phase-locked loop (PLL), een circuit dat synchroniseert met de frequentie van een referentieoscillatie en een signaal afgeeft met dezelfde of hogere frequentie. PLL's genereren 'kloksignalen, ' waarvan de oscillaties fungeren als een metronoom die een nauwkeurige timingreferentie biedt voor de harmonieuze werking van digitale apparaten.

Om hoogwaardige SoC-apparaten te realiseren, fabricageprocessen voor halfgeleiderelektronica moeten geavanceerder worden. Hoe kleiner het gebied om digitale schakelingen te implementeren, hoe beter de prestaties van het apparaat. Fabrikanten racen om steeds kleinere halfgeleiders te ontwikkelen. 7 nm-halfgeleiders (een enorme verbetering ten opzichte van hun 10 nm-voorganger) zijn al in productie, en methoden om 5 nm te bouwen worden nu bekeken.

Echter, in dit streven staat een groot knelpunt. Bestaande PLL's vereisen analoge componenten, die over het algemeen omvangrijk zijn en ontwerpen hebben die moeilijk te verkleinen zijn.

Wetenschappers van Tokyo Tech en Socionext Inc., onder leiding van prof. Kenichi Okada, hebben dit probleem aangepakt door een 'synthetiseerbare' fractionele-N PLL te implementeren, waarvoor alleen digitale logische poorten nodig zijn, en geen omvangrijke analoge componenten, waardoor het gemakkelijk kan worden toegepast in conventionele geminiaturiseerde geïntegreerde schakelingen.

Okada en team gebruikten verschillende technieken om het vereiste gebied te verkleinen, stroomverbruik en jitter - ongewenste tijdschommelingen bij het verzenden van digitale signalen - van hun synthetiseerbare PLL's. Om het gebied te verkleinen, ze gebruikten een ringoscillator, een compacte oscillator die eenvoudig kan worden verkleind. Om jitter te onderdrukken, ze verminderden de faseruis - willekeurige fluctuaties in een signaal - van deze ringoscillator, met behulp van 'injection locking' - het proces van het synchroniseren van een oscillator met een extern signaal waarvan de frequentie (of een veelvoud daarvan) dicht bij die van de oscillator ligt - over een breed scala aan frequenties. De lagere faseruis, beurtelings, verminderd stroomverbruik.

Het ontwerp van deze synthetiseerbare PLL verslaat dat van alle andere huidige state-of-the-art PLL's in veel belangrijke aspecten. Het bereikt de beste jitterprestaties met het laagste stroomverbruik en het kleinste oppervlak (zoals te zien is in afbeelding 1). "Het kerngebied is 0,0036 mm2, en de hele PLL is geïmplementeerd als één lay-out met een enkele voeding, " merkt Okada op. Verder, het kan worden gebouwd met behulp van standaard digitale ontwerptools, waardoor zijn snelle, weinig moeite, en goedkope productie, commercieel levensvatbaar maken.

Deze synthetiseerbare PLL kan eenvoudig worden geïntegreerd in het ontwerp van volledig digitale SoC's, en commercieel levensvatbaar is, waardoor het waardevol is voor de ontwikkeling van de veelgevraagde 5 nm-halfgeleider voor geavanceerde toepassingen, waaronder kunstmatige intelligentie, internet der dingen en vele anderen, waar hoge prestaties en een laag stroomverbruik de kritieke vereisten zouden zijn. Maar de bijdragen van dit onderzoek gaan verder dan deze mogelijkheden. "Ons werk demonstreert het potentieel van synthetiseerbare circuits. Met de hier gebruikte ontwerpmethodologie, andere bouwstenen van SoC's, zoals dataconverters, machtsbeheerkringen, en draadloze zendontvangers, zou ook synthetisch gemaakt kunnen worden. Dit zou de ontwerpproductiviteit aanzienlijk verhogen en de ontwerpinspanningen aanzienlijk verminderen, " legt Okada uit. Tokyo Tech en Socionext zullen hun samenwerking in dit dossier voortzetten om de miniaturisering van elektronische apparaten te bevorderen, waardoor de realisatie van nieuwere generatie technologieën mogelijk wordt.

Op weg naar een klimaatneutraal Europa:de landsector staat centraal

Op weg naar een klimaatneutraal Europa:de landsector staat centraal Nieuwe studie toont aan dat erosie van de zeebodem zich nu voordoet als landverlies aan de kust

Nieuwe studie toont aan dat erosie van de zeebodem zich nu voordoet als landverlies aan de kust De effecten van koolstofdioxide op luchtverontreiniging

De effecten van koolstofdioxide op luchtverontreiniging  5 Centrale thema's van de biologie

5 Centrale thema's van de biologie Sterke aardbeving schudt Kroatië, schade aan gebouwen in de hoofdstad

Sterke aardbeving schudt Kroatië, schade aan gebouwen in de hoofdstad

Hoofdlijnen

- DNA-replicatie vergelijken en contrasteren in prokaryoten en eukaryoten

- Familiebanden Snapper leveren nieuw bewijs op over mariene reservaten

- In Zuid Afrika, bijen voorkomen dat olifanten bomen vertrappen

- Doorbreken van peulvruchten gewas wilde relatieve barrière

- Wetenschappers vinden potentiële wapens voor de strijd tegen antibioticaresistentie

- Een rol van lipiden bij celdeling

- Soorten zenuwen in het menselijk lichaam

- Hypermutators zorgen ervoor dat pathogene schimmels sneller evolueren

- Hoe verlaat mRNA de kern?

- Natuurkundigen maken zeer efficiënte raketbrandstof

- Hoe het Europa vergaat met de doelstellingen voor hernieuwbare energie

- Koffieclash brouwen in China:startup Luckin neemt het op tegen Starbucks

- AMD's technologie voor nieuwe supercomputer voor Department of Energy

- Gigantische paraplu's verschuiven van handige luifel naar stevig stormscherm

Onderzoek geeft nieuw inzicht in het kapitaliseren van momentumbeleggen

Onderzoek geeft nieuw inzicht in het kapitaliseren van momentumbeleggen Thaise dinosaurus is een neef van T. rex

Thaise dinosaurus is een neef van T. rex Wiskunde relevant maken voor de klimaatstakingen

Wiskunde relevant maken voor de klimaatstakingen Soorten metalen die magneten aantrekken

Soorten metalen die magneten aantrekken Banen van oude sterren vragen om heroverweging van de evolutie van de Melkweg

Banen van oude sterren vragen om heroverweging van de evolutie van de Melkweg Uber trekt zich terug op waardering met IPO-prijzen

Uber trekt zich terug op waardering met IPO-prijzen Engineering team ontwikkelt nieuwe aanpak om loodverontreiniging in water te beperken

Engineering team ontwikkelt nieuwe aanpak om loodverontreiniging in water te beperken SpaceX klaar om NASA's nieuwe planeetjager te vernietigen, TESS

SpaceX klaar om NASA's nieuwe planeetjager te vernietigen, TESS

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com