Wetenschap

Nieuwe standaard maakt het mogelijk om gestapelde matrijzen in 3D-geïntegreerde schakelingen te verbinden met testapparatuur

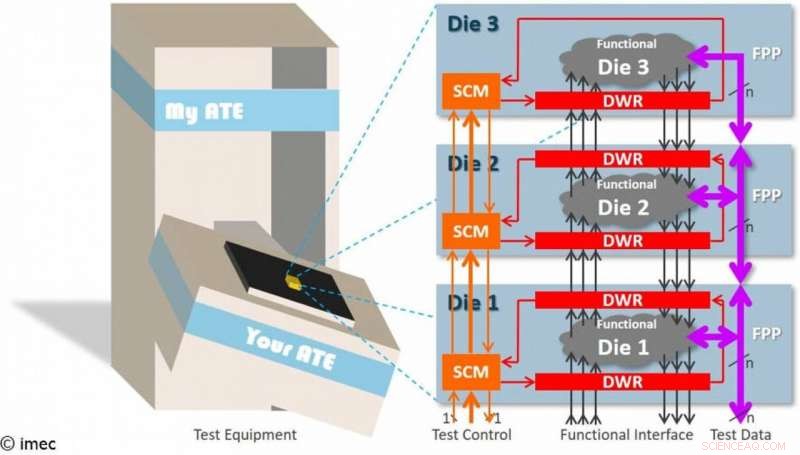

Conceptuele doorsnede van een 3D-IC bestaande uit drie gestapelde matrijzen. Testapparatuur stuurt teststimuli naar en ontvangt testreacties van de externe interface van de 3D-IC die zich onderaan de stapel bevindt. De IEEE Std 1838™-2019 design-for-test-elementen in de verschillende dies vormen een consistente testtoegangsarchitectuur waardoor de testapparatuur toegang heeft tot elke die in de stack. Krediet:IMEC

Deze week, IMEC, een wereldwijd toonaangevend onderzoeks- en innovatiecentrum op het gebied van nano-elektronica en digitale technologieën, heeft aangekondigd dat IEEE Std 1838TM-2019 - onlangs goedgekeurd door de IEEE Standards Association - vanaf februari 2020 zal worden opgenomen in IEEE Xplore Digital Library. Met de nieuwe standaard kunnen matrijzenmakers matrijzen ontwerpen die, indien aan deze norm wordt voldaan, vormen, eenmaal gestapeld in een 3-D-IC door een stapelintegrator, een consistente testtoegangsarchitectuur op stackniveau. De standaardisatie-inspanning van de 3-D-DfT (design-for-test) werd geïnitieerd door IMEC.

3-D-IC's benutten de verticale dimensie voor verdere integratie door matrijzen op elkaar te stapelen als een manier om het momentum van de wet van Moore in stand te houden. Eric Beyne, fellow en programmadirecteur 3-D System Integration bij IMEC, zegt, "Vooruitgang in waferverwerking en stapelassemblagetechnologieën creëren een schat aan verschillende stapelarchitecturen. Dit veroorzaakt een sterke toename van het aantal potentiële momenten waarop testen op fabricagefouten kunnen worden uitgevoerd:pre-bond (vóór stapelen), mid-bond (op gedeeltelijke stapels), post-bond (op volledige stapels), en laatste test (op verpakte 3-D-IC's). Testapparatuur maakt contact met IC's via de externe interface via sondenaalden of op de testaansluiting. In een stansstapel, die externe interface bevindt zich meestal in de onderste matrijs van de stapel. Om ervoor te zorgen dat de testapparatuur teststimuli kan leveren aan en reacties kan ontvangen van de verschillende matrijzen in de stapel, samenwerking van de onderliggende matrijzen is vereist om testtoegang te verlenen tot de die momenteel wordt getest."

Een IEEE-werkgroep voor het standaardiseren van 3-D-DfT werd in 2011 opgericht door Erik Jan Marinissen, wetenschappelijk directeur bij IMEC in Leuven, België en hij diende als eerste voorzitter. In recente jaren, Adam Kro, hoofd R&D-ingenieur in de Design Group bij Synopsys, is als huidige voorzitter van de werkgroep de drijvende kracht geweest.

Amit Sanghani, vice-president engineering in de Design Group bij Synopsys in Mountain View, Californië, VS verklaarde:"3-D-IC is een belangrijke technologie om de volgende golf van innovatie te leveren, aangezien de industrie voorbij 7nm schaalt. Momenteel, die kunnen afkomstig zijn van verschillende leveranciers met onsamenhangende DfT-architecturen.

De nieuwe standaard bestaat uit drie hoofdelementen. (1) DWR, het matrijswikkelregister:scan kettingen aan de rand van elke matrijs in de stapel om modulair testen van de binnenkant van elke matrijs en van de verbindingen tussen elk paar aangrenzende matrijzen mogelijk te maken. (2) SCM, het seriële besturingsmechanisme:een single-bit testbesturingsmechanisme dat instructies naar de stapel transporteert om de testmodi van de verschillende matrijswikkelaars te besturen. (3) FPP, de optionele flexibele parallelle poort, d.w.z., een schaalbaar multi-bit testtoegangsmechanisme om de grote hoeveelheden gegevens die typisch zijn voor productietests, efficiënt op en neer door de matrijsstapel te transporteren. Hoewel DWR en SCM gebaseerd zijn op bestaande DfT-standaarden, de FPP is echt nieuw voor IEEE Std 1838.

Wolfgang Meijer, senior groepsdirecteur R&D bij Cadence Design Systems in San Jose, Californië, ONS., zegt, "Een DfT-standaard zoals IEEE Std 1838 is belangrijk voor de industrie. Matrijzenmakers weten wat ze moeten leveren, en stackintegrators weten wat ze kunnen verwachten. Bovendien, EDA-leveranciers zoals Cadence kunnen hun toolondersteuning richten op architecturen die voldoen aan de nieuwe standaard. Het is goed dat er enige door de gebruiker gedefinieerde schaalbaarheid met de standaard is, aangezien het 3-D-IC-veld zo breed is - een rigide 'one-size-fits-all'-standaard zou niet werken."

Junlin Huang, manager van een 150 man sterk DfT-team van HiSilicon in Shenzhen, China, zegt, "Per jaar, we doen DfT-insertie en automatische testpatroongeneratie (ATPG) voor tientallen zeer grote en complexe digitale chipontwerpen in de meest geavanceerde technologieën. Nutsvoorzieningen, deze producten maken gebruik van 3D-technologie en mijn DfT-team moet klaar zijn om de bijbehorende DfT- en ATPG-uitdagingen aan te kunnen. IEEE Std 1838 zal ons daarbij helpen."

Vanaf februari 2020, de nieuwe standaard IEEE Std 1838 zal beschikbaar zijn via IEEE Xplore voor abonnees van IEEE-standaarden en voor aankoop door iedereen.

Onderzoekers ontwikkelen chip die testen en traceren voor COVID-19 verbetert

Onderzoekers ontwikkelen chip die testen en traceren voor COVID-19 verbetert Wetenschappers publiceren een compleet overzicht van sulfonimide-dendrimeren

Wetenschappers publiceren een compleet overzicht van sulfonimide-dendrimeren De regels overtreden:zware chemische elementen veranderen de theorie van de kwantummechanica

De regels overtreden:zware chemische elementen veranderen de theorie van de kwantummechanica Het mysterie van het moeilijkste materiaal van de natuur kraken

Het mysterie van het moeilijkste materiaal van de natuur kraken Wat is een alkalische oplossing

Wat is een alkalische oplossing

Wereldwijde database voor efficiënt watergebruik

Wereldwijde database voor efficiënt watergebruik sociale afstand, duurzame steden en het opbouwen van capaciteit voor de volksgezondheid

sociale afstand, duurzame steden en het opbouwen van capaciteit voor de volksgezondheid Antarctische landschapsinzichten houden voorspellingen over ijsverlies op de radar

Antarctische landschapsinzichten houden voorspellingen over ijsverlies op de radar NASA-sneeuwcampagne loopt af voor 2021

NASA-sneeuwcampagne loopt af voor 2021 Wetenschappers onthullen reacties van verschillende biokorsten op opwarming en toegenomen droogte

Wetenschappers onthullen reacties van verschillende biokorsten op opwarming en toegenomen droogte

Hoofdlijnen

- Wat is de rol van de milt en het beenmerg in de bloedsomloop?

- Onderzoek details genetische resistentie tegen plotselinge dood syndroom in sojabonen

- Zenuwen controleren de bacteriële gemeenschap van het lichaam

- De voordelen van het bestuderen van cellen onder een lichtmicroscoop

- M-fase: wat gebeurt er in deze fase van de celcyclus?

- Beperkingen Enzymen die worden gebruikt in DNA-vingerafdrukken

- Misplaatste monarchen:clusters van vlinders in het noorden

- Voeding door mensen verandert het gedrag en de fysiologie van groene schildpadden op de Canarische Eilanden

- Begrazing van vee schaadt leefgebied van reuzenpanda's

- Onderzoekers ontwikkelen innovatieve, meer kosteneffectieve methode om medicijnen te maken

- De online strijd om de waarheid

- Uber begint bijna 7% onder de IPO-prijs te handelen

- Materialen verhoogde capaciteit, efficiëntie kan de lat voor waterstoftechnologie verlagen

- Tech moet worden behandeld als tabak, zegt Facebook-klokkenluider

Jupiters complexe voorbijgaande aurora's

Jupiters complexe voorbijgaande aurora's Startups schudden de slaperige scheermesmarkt wakker. Wat is het volgende?

Startups schudden de slaperige scheermesmarkt wakker. Wat is het volgende? Geoptimaliseerde analyses verminderen valse negatieven bij de detectie van nanodeeltjes

Geoptimaliseerde analyses verminderen valse negatieven bij de detectie van nanodeeltjes Opbouw naar superbloedmaan verduistert de finale

Opbouw naar superbloedmaan verduistert de finale De zon als een ster bestuderen om steruitbarstingen en exoplaneten te begrijpen

De zon als een ster bestuderen om steruitbarstingen en exoplaneten te begrijpen Daling van de vraag naar olie helpt de klimaatemissiedoelstellingen mogelijk niet

Daling van de vraag naar olie helpt de klimaatemissiedoelstellingen mogelijk niet EU kondigt strikte 5G-regels aan maar geen Huawei-verbod

EU kondigt strikte 5G-regels aan maar geen Huawei-verbod Erosie-instabiliteiten op landschapsschaal in het noorden van Gabilan Mesa, Californië

Erosie-instabiliteiten op landschapsschaal in het noorden van Gabilan Mesa, Californië

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com