Wetenschap

Demonstratie van snelle SOT-MRAM-geheugencel die compatibel is met 300 mm Si CMOS-technologie

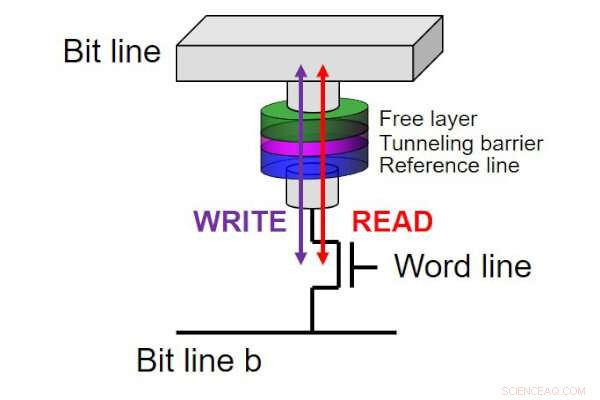

Schema van STT-MRAM-cel (Two Terminal Device). Krediet:CIES, Tohoku-universiteit

Onderzoekers van de Tohoku University hebben de demonstratie aangekondigd van een high-speed spin-orbit-torque (SOT) magnetoresistieve random access geheugencel die compatibel is met 300 mm Si CMOS-technologie.

De vraag naar low-power en high-performance geïntegreerde circuits (IC's) is toegenomen naarmate apparaten voor kunstmatige intelligentie (AI) en Internet-of-Things (IoT) op grotere schaal worden gebruikt. Met de huidige IC's puur op CMOS gebaseerde geheugens zoals embedded Flash-geheugen (eFlash) en statisch willekeurig toegankelijk geheugen (SRAM) zijn verantwoordelijk voor een groot deel van het stroomverbruik. Om het stroomverbruik te verlagen en tegelijkertijd hoge prestaties te behouden, magnetoresistieve random access memorys (MRAM's) zijn intensief ontwikkeld. Spin-transfer koppel MRAM's (STT-MRAM's) zijn de meest intensief ontwikkelde MRAM's. Grote halfgeleiderbedrijven hebben nu aangekondigd dat ze klaar zijn voor massaproductie van STT-MRAM voor eFlash-vervanging.

Onderzoekers streven ernaar om SRAM te vervangen door MRAM. Voor SRAM-vervanging, MRAM moet een snelle werking boven 500 MHz bereiken. Om aan de vraag te voldoen, een alternatief MRAM, zogenaamde spin-orbit torque MRAM (SOT-MRAM) werd voorgesteld, wat verschillende voordelen heeft voor snelle bediening. Door deze voordelen, SOT-MRAM is ook ontwikkeld; echter, de meeste laboratoriumonderzoeken richten zich op de fundamenten van SOT-apparaten. Om SRAM-vervanging door SOT-MRAM te realiseren, het is vereist om de hoge prestaties van een SOT-MRAM-geheugencel op een 300 mm CMOS-substraat aan te tonen. In aanvulling, het is noodzakelijk om het integratieproces voor SOT-MRAM te ontwikkelen, bijv. thermische tolerantie tegen 400 °C gloeien, wat een vereiste is van het standaard CMOS back-end-of-line proces.

-

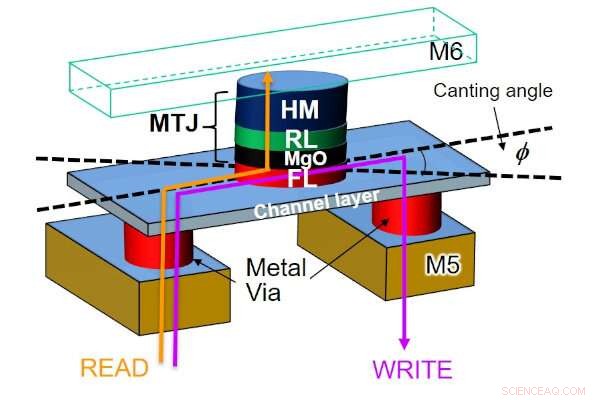

Een schema van de SOT-MRAM-cel (Three Terminal Device) Credit:CIES, Tohoku-universiteit

-

Een schematisch aanzicht van de gekantelde SOT-MRAM-cel. Krediet:CIES, Tohoku-universiteit

Het onderzoeksteam onder leiding van professoren Tetsuo Endoh en Hideo Ohno - de huidige president van Tohoku University - heeft een integratieproces ontwikkeld voor SOT-apparaten die compatibel zijn met 55 nm CMOS-technologie en vervaardigde SOT-apparaten op CMOS-substraten van 300 mm. Het nieuw ontwikkelde SOT-apparaat heeft tegelijkertijd een snelle omschakeling tot 0,35 ns en een voldoende hoge thermische stabiliteitsfactor (E/k B T 70) voor de snelle niet-vluchtige geheugentoepassingen met robuustheid tegen uitgloeien bij 400 °C. Op basis van deze prestatie het onderzoeksteam heeft het SOT-apparaat geïntegreerd met CMOS-transistors en heeft uiteindelijk de snelle werking in complete SOT-MRAM-geheugencellen gedemonstreerd.

Deze prestaties hebben de problemen aangepakt om SOT-MRAM praktisch te maken voor commerciële toepassingen en bieden zo een manier om SRAM te vervangen door SOT-MRAM, die zal bijdragen aan de realisatie van hoogwaardige elektronica met een laag stroomverbruik.

De resultaten zullen worden gepresenteerd op de IEEE International Electron Devices Meeting 2019 in San Francisco, 7-11 december 2019.

NASA volgt tropische depressie Cristobal op weg naar Grote Meren

NASA volgt tropische depressie Cristobal op weg naar Grote Meren VN-rapport:Toegenomen opwarming nadert overeengekomen grens

VN-rapport:Toegenomen opwarming nadert overeengekomen grens tientallen doden, vermist in Japan omdat hevige regen overstromingen veroorzaakt, modderstromen

tientallen doden, vermist in Japan omdat hevige regen overstromingen veroorzaakt, modderstromen Ecosysteem van vijvers voor kinderen

Ecosysteem van vijvers voor kinderen  Vergelijking van mondiale klimatologieën bevestigt opwarming van de mondiale oceaan

Vergelijking van mondiale klimatologieën bevestigt opwarming van de mondiale oceaan

Hoofdlijnen

- Wat zijn endorfines?

- In het laboratorium gekweekt vlees zou de mensheid een ernstig moreel falen kunnen laten negeren

- Wat is het pad van het licht door het oog?

- De sleutelrol van enzymen in de embryonale ontwikkeling begrijpen

- Hoe kan iemand 11 dagen wakker blijven?

- Een nieuwe rol voor insuline als vitale factor bij het in stand houden van stamcellen

- "Recessive Allele: What is it?", 3, [[& Waarom gebeurt het? (met eigenschappenkaart)

- Auxine zorgt voor bladafvlakking

- Kenmerken van Twins

Subtropische storm Andrea springt in het geweer als de eerste storm van het Atlantische seizoen van 2019

Subtropische storm Andrea springt in het geweer als de eerste storm van het Atlantische seizoen van 2019 Een op insecten geïnspireerde drone vervormt bij impact

Een op insecten geïnspireerde drone vervormt bij impact Verschil tussen gekamd katoen en katoen

Verschil tussen gekamd katoen en katoen  Octupole hoektoestand in een driedimensionaal topologisch circuit

Octupole hoektoestand in een driedimensionaal topologisch circuit Bacteriën onder de loep nemen

Bacteriën onder de loep nemen Trek uw eigen elektroden om de ontwikkeling van microdetectieapparatuur te versnellen

Trek uw eigen elektroden om de ontwikkeling van microdetectieapparatuur te versnellen De elektriciteitssector in Australië moet de CO2-uitstoot tegen 2030 met 45% verminderen

De elektriciteitssector in Australië moet de CO2-uitstoot tegen 2030 met 45% verminderen Op weg om een betaalbare auto te maken, Tesla schrapt banen

Op weg om een betaalbare auto te maken, Tesla schrapt banen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway | Italian |

-

Wetenschap © https://nl.scienceaq.com