Wetenschap

Een dynamische camouflagebenadering om diefstal van intellectueel eigendom te voorkomen

De globalisering van de IC-toeleveringsketen heeft kwetsbaarheden veroorzaakt in verschillende stadia van de IC-productie. Hier, de fasen van de rode zones zijn niet vertrouwd en kunnen door een aanvaller worden misbruikt. Krediet:Rangarajan et al.

In recente jaren, hardwaregerichte beveiligingsbedreigingen zijn ontstaan in verschillende stadia van de supply chain van geïntegreerde schakelingen (IC). Dit heeft de verspreiding van verschillende kwaadaardige aanvallen mogelijk gemaakt, zoals intellectuele eigendom (IP) piraterij, illegale overproductie van IC's, en het inbrengen van hardware-trojans.

Van alle bestaande verdedigingen tegen IP-piraterij, tot nu toe is alleen logische vergrendeling gevonden om effectieve end-to-end bescherming te bieden. Om deze uitdagingen aan te gaan, een onderzoeksteam van het New York University Center for Cybersecurity en Quantum Nanoelectronics Lab heeft een dynamische camouflagebenadering ontwikkeld om IP-reverse engineering in alle stadia van de toeleveringsketen te dwarsbomen.

"De globalisering van de supply chain van geïntegreerde schakelingen heeft geleid tot de uitbesteding van verschillende stappen van de productie van micro-elektronische chips, "Nikhil Rangarajan, een van de onderzoekers die het onderzoek heeft uitgevoerd, vertelde TechXplore . "Chips worden doorgaans ontworpen en/of ingekocht in één land, vervaardigd in een andere, en uiteindelijk elders getest en verpakt. Deze wereldwijde keten biedt aanvallers veel mogelijkheden om het onderliggende IP te stelen, overproductie, of zelfs kwaadaardige modificaties invoegen die bekend staan als hardware-trojans."

Volgens schattingen, de halfgeleiderindustrie verliest elk jaar miljarden dollars door IP-diefstal. Om deze schade te beperken, het onderzoek van Rangarajan en zijn collega's richt zich specifiek op het voorkomen van IE-diefstal.

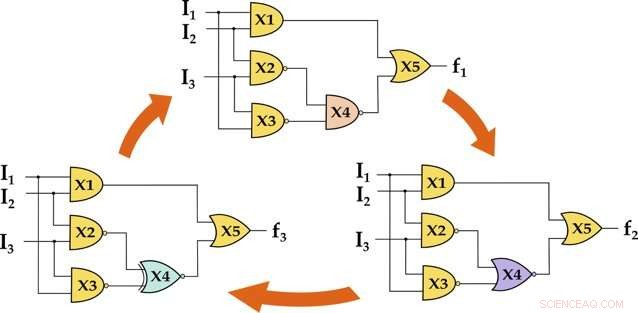

Dynamisch schakelen van polymorfe circuits on-the-fly. Krediet:Rangarajan et al.

"De inspiratie voor ons idee kwam uit de natuur, waar sommige dieren zoals octopus hun fysieke verschijning kunnen veranderen om zich aan te passen aan hun omgeving om detectie door prooien of roofdieren te voorkomen, " legde Rangarajan uit. "We dachten:waarom kunnen de elektronische circuits die we willen beschermen niet ook dynamisch veranderen om detectie door een aanvaller te voorkomen?"

Bestaande verdedigingsmechanismen ter voorkoming van IP-diefstal, zoals statische camouflage, vereisen dat de ontwerper vertrouwt op de gieterij die opdracht heeft gegeven voor de fabricage van de chip. Integendeel, het dreigingsmodel van Rangarajan en zijn collega's gaat ervan uit dat een aanvaller zich ook in de gieterij of in de testfaciliteit kan bevinden, of mogelijk een eindgebruiker zijn.

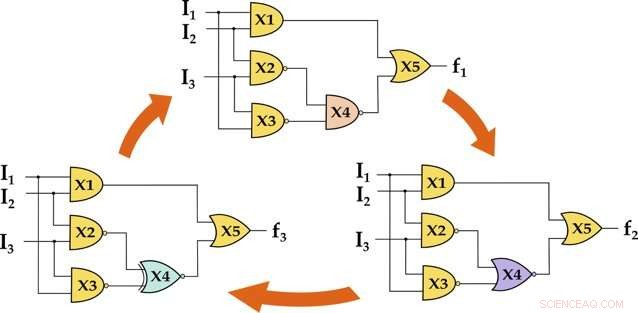

"Door gebruik te maken van aangeboren eigenschappen zoals polymorfisme, multifunctionaliteit, en herconfigureerbaarheid na fabricage aangeboden door opkomende spintronische apparaten, zoals het magneto-elektrische spinbaan (MESO) apparaat, we waren in staat om dynamische camouflage te bereiken, "Satwik Patnaik, een andere onderzoeker die bij het onderzoek betrokken was, vertelde TechXplore. "Polymorfisme is bedoeld in de specifieke middelen waarmee het apparaat tijdens runtime gemakkelijk verschillende Booleaanse functies kan implementeren, waarbij de functionaliteit wordt bepaald door een intern of extern controlemechanisme."

In het door de onderzoekers opgestelde schema een potentieel kwaadaardige gieterij fabriceert de logische poorten als "zwarte dozen, " die pas door de ontwerper kan worden geconfigureerd als het fabricageproces is voltooid. Dit voorkomt dat een aanvaller binnen de gieterij de beoogde functionaliteit van de chip die in fabricage is, ontcijfert, zoals het nog moet worden geconfigureerd.

Dynamisch camoufleren is mogelijk met behulp van nieuwe spintronische poorten zoals MESO-poorten. Deze poorten kunnen meerdere Booleaanse functionaliteiten in één apparaat implementeren en kunnen er ook tussen schakelen tijdens runtime. Krediet:Rangarajan et al.

"Deze eigenschap 'herconfigureerbaar na fabricage' biedt ook bescherming tegen niet-vertrouwde testfaciliteiten, aangezien de chip kan worden geconfigureerd voor elke dummy-functionaliteit die een aanvaller niet kent en kan worden hersteld naar de echte functionaliteit zodra de test is uitgevoerd, " legde Patnaik uit. "Kortom, terwijl eerdere werken in IC-camouflage statisch zijn en de gieterij moeten vertrouwen, ons schema vereist niet dat de ontwerper de gieterij of de testfaciliteit vertrouwt."

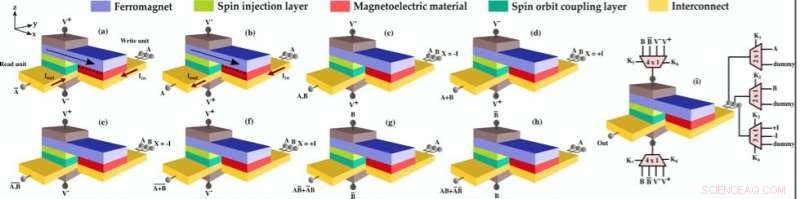

De onderzoekers evalueerden de effectiviteit van hun aanpak bij het tegengaan van state-of-the-art test-data mining-aanvallen, zoals HackTest, en zijkanaalanalyse, waar tegenstanders de functionaliteit van het IP proberen te ontcijferen. Ze onderzochten ook de prestaties met krachtige Booleaanse verzadigingsaanvallen, inclusief SAT en geschatte SAT (AppSAT), die typisch de voorkeur hebben van eindgebruikers.

Hun dynamische camouflagebenadering leverde veelbelovende resultaten op in al deze tests. In de toekomst, de onderzoekers denken dat het kan helpen om aanvallers binnen niet-vertrouwde gieterijen of testfaciliteiten te dwarsbomen.

"Ons schema maakt gebruik van de unieke eigenschappen van op spin gebaseerde apparaten, " legde Rangarajan uit. "Deze eigenschappen, vooral polymorfisme, niet kunnen worden geboden door de huidige CMOS-technologieën, vanwege de fundamentele beperkingen van CMOS-apparaten. We willen ook benadrukken dat het algemene idee van dynamische camouflage kan worden geïmplementeerd met andere opkomende apparaten, zolang ze vergelijkbare eigenschappen hebben."

Een Booleaanse verzadigingsaanval op een dynamisch gecamoufleerd circuit kan gemakkelijk een onjuiste sleutel opleveren en de aanvaller misleiden. Krediet:Rangarajan et al.

Om de implementatie van hun verdedigingstechniek te bevorderen, de onderzoekers stellen zich ook een hybride CMOS-spin-gebaseerde integratie voor. Deze integratie zou de goedkeuring en acceptatie van hun schema kunnen vergemakkelijken, evenals van apparaten die dit ondersteunen. Volgens de onderzoekers is verschillende academische studies gaan momenteel in vergelijkbare richtingen.

Rangarajan en zijn collega's zijn nu van plan om de implicaties te onderzoeken van het gebruik van runtime-polymorfisme om benaderende logische circuits te beschermen, die de afgelopen jaren veel aandacht hebben gekregen. Dit soort circuits ruilen uitgangsnauwkeurigheid in voor een sterke vermindering van de vermogensdissipatie.

"Vooral met de komst van het Internet-of-Things (IoT), wij zijn van mening dat de bescherming van geschatte computerchips ook essentieel is, gezien het feit dat ze alom de voorkeur hebben om te worden gebruikt in systemen die een laag stroomverbruik vereisen, " zei Rangarajan. "We zijn ook van plan om de veerkracht van ons plan te evalueren onder andere aanvalsscenario's, om meer vertrouwen te krijgen in onze aanpak."

© 2018 Wetenschap X Netwerk

Modulerende spiraalvormige nanostructuren in vloeibare kristalfase door moleculair ontwerp

Modulerende spiraalvormige nanostructuren in vloeibare kristalfase door moleculair ontwerp Wat veroorzaakt een lager vriespunt?

Wat veroorzaakt een lager vriespunt?  Onderzoekers maken kunstmatig parelmoer met behulp van bacteriën

Onderzoekers maken kunstmatig parelmoer met behulp van bacteriën Wetenschappers identificeren nieuwe katalysatoren voor efficiëntere watersplitsing

Wetenschappers identificeren nieuwe katalysatoren voor efficiëntere watersplitsing Onderzoekers tikken lasers om haaienhuid na te bootsen, andere natuurlijke oppervlakken

Onderzoekers tikken lasers om haaienhuid na te bootsen, andere natuurlijke oppervlakken

Koraalrifoases bieden een sprankje hoop

Koraalrifoases bieden een sprankje hoop Arseen in huishoudelijk bronwater kan twee miljoen mensen in de VS treffen

Arseen in huishoudelijk bronwater kan twee miljoen mensen in de VS treffen Lavaverspreiding doet vrezen voor meer schade op Spaans eiland

Lavaverspreiding doet vrezen voor meer schade op Spaans eiland Onderzoek suggereert dat oesters een hotspot zijn voor het verminderen van vervuiling door nutriënten

Onderzoek suggereert dat oesters een hotspot zijn voor het verminderen van vervuiling door nutriënten Mos dat arseen uit drinkwater kan verwijderen ontdekt

Mos dat arseen uit drinkwater kan verwijderen ontdekt

Hoofdlijnen

- Hoe de lengte van DNA-fragmenten te berekenen

- Japanse dierentuin rouwt om dood van verliefde pinguïn

- Orkaan verscheurde het gerenommeerde onderzoekscentrum van Monkey Island

- Strategie voor celdeling gedeeld door alle domeinen van het leven

- De voordelen van over jezelf praten in de derde persoon

- Het ontrafelen van de mechanismen die de celgroei en -grootte regelen

- Een model waarmee planten hun fotosynthetische stofwisseling aanpassen aan de lichtintensiteit

- Soorten organismen die van plantencellen zijn gemaakt

- Onderzoekers ontdekken hoe planten op moleculair niveau reageren op veranderingen in licht

- Verkeerde informatie en vooroordelen besmetten sociale media, zowel opzettelijk als per ongeluk

- Japanse bedrijven worden aangeklaagd wegens vermeende manipulatie van maglev-biedingen

- Klein, snel, nauwkeurige technologie op de radar

- Machine learning-aanpak voor laaggedoseerde CT-beeldvorming levert superieure resultaten op

- Online mythbusters vechten tegen de stroom van nepnieuws in India

Wat is een riviervloed?

Wat is een riviervloed?  Afbeelding:Palmolieplantages in Borneo gezien vanuit een baan om de aarde

Afbeelding:Palmolieplantages in Borneo gezien vanuit een baan om de aarde Verzuring van de oceaan bereikt niveaus die in 14 miljoen jaar niet zijn gezien

Verzuring van de oceaan bereikt niveaus die in 14 miljoen jaar niet zijn gezien Wetenschappers beoordelen het binnendringen van zout water in bronwater langs de kust van Rhode Island

Wetenschappers beoordelen het binnendringen van zout water in bronwater langs de kust van Rhode Island Ultradun en ultrasnel:wetenschappers pionieren met nieuwe techniek voor tweedimensionale materiaalanalyse

Ultradun en ultrasnel:wetenschappers pionieren met nieuwe techniek voor tweedimensionale materiaalanalyse Problemen met een elektromotor oplossen Hum

Problemen met een elektromotor oplossen Hum Nieuwe technologie voor het eerste experiment met de grootste bron van röntgenstraling ter wereld

Nieuwe technologie voor het eerste experiment met de grootste bron van röntgenstraling ter wereld Hoe het volume en de omtrek van een cirkel te berekenen

Hoe het volume en de omtrek van een cirkel te berekenen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com