Wetenschap

CNT wrap-gate-transistors kunnen de schaling van de transistorprestaties verlengen

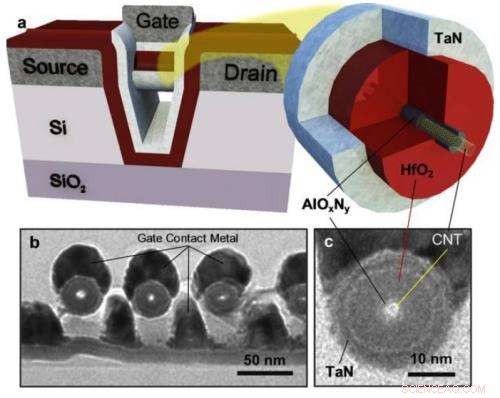

(a) Dwarsdoorsnedediagram van de CNTFET die illustreert hoe het CNT-kanaal (afgesneden diagram rechts weergegeven) over de siliciumgeul wordt opgehangen en aan weerszijden wordt gecontacteerd door de bron / afvoer. (b) en (c) tonen transversale TEM-afbeeldingen van nanobuisjes met een gate-all-round geometrie, die de nanobuisjes beschermt tegen de invloed van naburige apparaten en verdwaalde ladingen. Krediet:Franklin, et al. ©2013 American Chemical Society

(Phys.org) —Gedurende de jaren '70, jaren '80 en '90, De prestaties van de transistor namen voortdurend toe volgens enkele eenvoudige schaalregels. Deze regels stellen dat de grootte van de transistor en de voedingsspanning moeten afnemen naarmate de vermogensdichtheid constant blijft, resulterend in een algehele verbetering van de prestaties. Echter, fysieke beperkingen stopten met het opschalen van de voedingsspanning in de vroege jaren 2000, dus de eenvoudige schaalregels zijn niet langer van toepassing. Nu gaat elke prestatieverbetering ten koste van een toename van het stroomverbruik, zodat de prestaties van de transistor sinds het midden van de jaren 2000 zijn afgevlakt.

Nu in een nieuwe studie, onderzoekers van het IBM T.J. Watson onderzoekscentrum in Yorktown Heights, New York, hebben het potentieel van koolstofnanobuizen benut als een manier om de schaalregels uit te breiden en verdere prestatieverbeteringen in transistors te bereiken. Op een dag, transistors gemaakt van koolstofnanobuizen kunnen de ruggengraat vormen van veel van onze elektronische apparaten, inclusief smartphones en tablets.

De schalingsonderbreking die transistors in het afgelopen decennium tegenkwamen, was grotendeels te wijten aan de fysieke kenmerken van de transistors zelf, die silicium-metaaloxide-halfgeleider-veldeffecttransistoren (MOSFET's) zijn. In de laatste paar jaren, onderzoekers hebben de mogelijkheid onderzocht om MOSFET's te vervangen door koolstofnanobuis-veldeffecttransistoren (CNTFET's). Deze transistors hebben al veel aantrekkelijke eigenschappen laten zien, inclusief goede prestaties bij lage spanningen met kanaalcomponenten van minder dan 10 nm lang - een schaal die silicium MOSFET's fysiek niet kunnen bereiken met goede prestaties.

"Er zijn twee belangrijke redenen waarom CNTFET's voordelen bieden die MOSFET's niet kunnen:1) De CNT's zijn ultradunne halfgeleiders (~ 1 nm), waardoor ze kunnen worden geïntegreerd in agressief geschaalde apparaten zonder de controle over de stroom in het kanaal te verliezen; en 2) CNTFET's kunnen werken bij lage voedingsspanningen, wat betekent dat ze het niveau van elektrische stroom kunnen leveren dat nodig is om geïntegreerde schakelingen aan te sturen met een lagere spanning dan MOSFET's ooit kunnen bereiken, " vertelde co-auteur en IBM-onderzoeker Aaron D. Franklin: Phys.org . "Al bijna een decennium lang er is weinig tot geen vermindering van de voedingsspanning voor MOSFET-technologieën geweest - CNTFET's zijn een van de beste opties om die trend te veranderen."

Echter, om te concurreren met MOSFETS, CNTFET's vereisen nog een aantal belangrijke vorderingen, inclusief een schaalbare poort die zichzelf kan uitlijnen op de bron- en afvoercontacten, complementaire n- en p-type apparaten (die verschillen door polarisatie), en compatibiliteit met de draadverwerking die nodig is om circuits te bouwen.

In hun krant de onderzoekers hebben aan alle drie deze vereisten voldaan door een CNT-transistor te bouwen met een poort die het CNT-kanaal volledig omringt. De onderzoekers leggen uit dat deze gate-all-around (GAA)-geometrie ideaal is omdat het de CNT beschermt tegen koppeling met naburige CNT's en tegen verdwaalde ladingen die op zo'n kleine schaal te dichtbij komen en instabiliteit veroorzaken.

"Het grootste belang van dit werk is de implementatie van een poort die de cilindrische CNT-kanalen volledig omhult, Franklin zei. "Omdat nanobuisjes slechts enkele moleculen zijn met een diameter van ~ 1 nm en zijn gemaakt van een enkele schil van atomen (hol aan de binnenkant), ze zijn erg gevoelig voor elektrische storingen in hun omgeving. Door elk CNT-kanaal in zijn eigen diëlektrische en metalen poort te wikkelen, ze raken geïsoleerd van dergelijke verstoringen en brengen de apparaten een stap dichter bij een reproduceerbare en betrouwbare technologie."

De omhullende poort is ook zelf-uitgelijnd met de bron- en afvoercontacten zonder dat lithografie nodig is. Als een zelf-uitlijnende poort, het overlapt of overlapt de bron/afvoer niet, maar past bijna perfect, wat belangrijk is voor het verzekeren van een goed pad voor de ladingsstroom. De onderzoekers konden de poortlengte ook verkleinen tot 20 nm, en voorspellen dat verdere schaalvergroting mogelijk is voor nog kleinere CNT-kanalen.

De poort kan ook worden gebruikt om zowel n- als p-type apparaten te realiseren door verschillende diëlektrische materialen te gebruiken om de polariteit te veranderen. Hoewel het n-type apparaat betere prestaties levert dan het p-type apparaat, de onderzoekers voorspellen dat dit laatste kan worden verbeterd door dunnere spacer-regio's te maken, aangezien deze afstandhouders een barrière vormen voor het laadtransport.

De onderzoekers voerden ook kwantumsimulaties van de CNTFET uit om hun begrip van de werking van het apparaat te bevestigen. De simulatieresultaten kwamen nauw overeen met de experimentele resultaten, en stelden de onderzoekers ook in staat om de impact van verschillende variabelen op de apparaatprestaties te projecteren, inclusief spacer dikte en doping. Deze wijzigingen zouden theoretisch de op-stroom kunnen verhogen, verminder de uit-stroom, en een subthreshold swing leveren die zeer dicht bij de theoretische limiet van 60 mv/dec ligt, wat betekent dat de transistor zeer snel kan schakelen tussen aan en uit.

Vooruit gaan, de resultaten tonen aan dat arrays van CNT's kunnen worden geïntegreerd in schaalbare, zelf-uitgelijnde n- en p-type transistors met ideale omhullende poorten. De onderzoekers voorspellen dat, met verdere optimalisatie, deze CNTFET's zouden ooit kunnen dienen als laagspanning, high-performance transistors die een wijdverbreide impact hebben op toekomstige toepassingen.

"Bij IBM, we hebben de afgelopen jaren aangetoond dat u uitstekende CNTFET-prestaties kunt bereiken tot kanaallengtes van minder dan 10 nm en dat u dit nu kunt doen in een technologisch compatibele wrap-gate-structuur, Franklin zei. "De grootste uitdaging op apparaatniveau is om de injectie van dragers bij de metaal-CNT-contacten van de apparaten te verbeteren. Wanneer contacten worden geschaald naar de benodigde kleine afmetingen voor een technologie, de contactweerstand stijgt aanzienlijk en moet worden aangepakt. Hoewel dit probleem niet uniek is voor CNTFET's (MOSFET's van alle typen lijden op dezelfde manier), het is een obstakel dat een oplossing vereist om toegang te krijgen tot het volledige potentieel van een CNT-technologie.

"Buiten het apparaatgebied, de twee belangrijkste obstakels voor materialen zijn om de zuiverheid en isolatie van halfgeleidende CNT's van hun metalen tegenhangers te blijven vergroten en om de CNT's nauwkeurig op precieze locaties op een substraat te assembleren. Op beide gebieden is het afgelopen jaar een indrukwekkende vooruitgang geboekt, zowel van IBM en andere onderzoeksgroepen."

© 2013 Fys.org. Alle rechten voorbehouden.

Grotere steden hebben een kleinere watervoetafdruk dan minder bevolkte tegenhangers

Grotere steden hebben een kleinere watervoetafdruk dan minder bevolkte tegenhangers Canadese gletsjers leveren nu een belangrijke bijdrage aan de verandering van de zeespiegel

Canadese gletsjers leveren nu een belangrijke bijdrage aan de verandering van de zeespiegel Nieuw boek schetst hoe steden zich organiseren om duurzaamheidsinitiatieven te realiseren

Nieuw boek schetst hoe steden zich organiseren om duurzaamheidsinitiatieven te realiseren Terugkeer van vulkanische vervuiling gekoppeld aan sprong in gevallen van luchtwegaandoeningen

Terugkeer van vulkanische vervuiling gekoppeld aan sprong in gevallen van luchtwegaandoeningen Kelps-recordreis stelt Antarctische ecosystemen bloot aan verandering

Kelps-recordreis stelt Antarctische ecosystemen bloot aan verandering

Hoofdlijnen

- Wat zijn drie primaire doelen van mitose?

- De smerigste beesten van de natuur te zien in Londen

- Wie ontdekte hemoglobine?

- Antibiotica uit een moleculaire puntenslijper

- Hoe de immuunrespons bijdraagt aan Homeostasis

- Een enzym dat de vorming van het DNA katalyseert Molecuul

- Lijst met genotypes

- De ellende van Merkel neemt toe als minister van Landbouw orders negeert (update)

- Onderzoek naar acceptatie van evolutie voor beter wetenschappelijk onderwijs

- Gelaagde vloeistoffen rangschikken nanodeeltjes in bruikbare configuraties

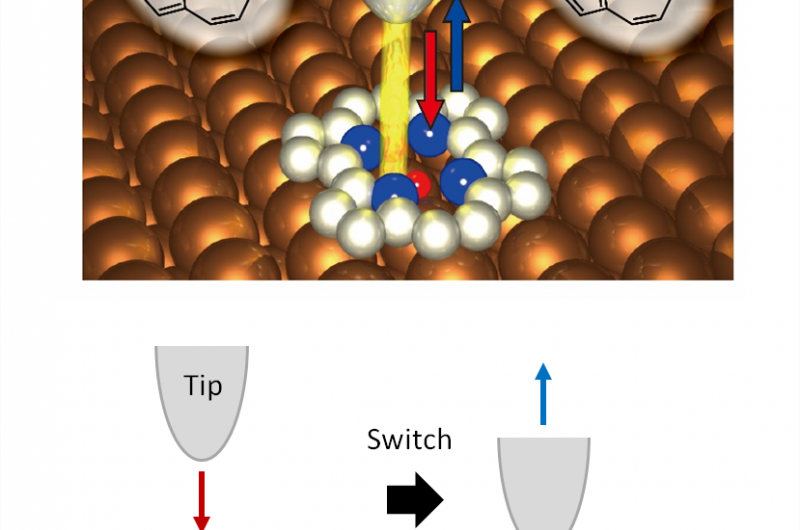

- Een schakelaar met één molecuul indrukken

- Onderzoeksteams ontwikkelen rollende microcapsules om microscopisch kleine defecten in oppervlakken te herstellen

- Atomic mismatch creëert nano-halters

- Onderzoek toont het potentieel aan van koolstofnanobuisjes om elektronische circuits te koelen

Waarom COVID-19 onze steden misschien niet zoveel verandert als we verwachten

Waarom COVID-19 onze steden misschien niet zoveel verandert als we verwachten De voordelen van Simple Distillation

De voordelen van Simple Distillation In de Braziliaanse pampa's, een Trias Park bloeide ooit

In de Braziliaanse pampa's, een Trias Park bloeide ooit Hoe COVID-19 de impact van desinformatie op de samenleving onthult

Hoe COVID-19 de impact van desinformatie op de samenleving onthult Wat managers en medewerkers moeten weten over het weer aan het werk gaan na quarantaine

Wat managers en medewerkers moeten weten over het weer aan het werk gaan na quarantaine Facebook overweegt kosten in rekening te brengen voor toegang tot gebruikersgegevens

Facebook overweegt kosten in rekening te brengen voor toegang tot gebruikersgegevens Onderzoek toont aan dat een derde van de beschermde gebieden ter wereld is aangetast door menselijke activiteiten

Onderzoek toont aan dat een derde van de beschermde gebieden ter wereld is aangetast door menselijke activiteiten Zelfmontage, biomimetische composieten hebben ongebruikelijke elektrische eigenschappen

Zelfmontage, biomimetische composieten hebben ongebruikelijke elektrische eigenschappen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | German | Dutch | Danish | Norway | Swedish |

-

Wetenschap © https://nl.scienceaq.com