Wetenschap

Transistors naar een nieuwe dimensie brengen

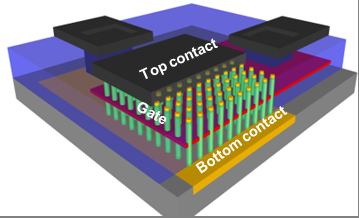

Diagram van een 3D-nanotransistor die de poort (rood) toont die de verticale nanodraden (groen) omringt en de contacten aan de uiteinden van elke nanodraad (beige) scheidt. Krediet:© X-L Han en G. Larrieu

Een nieuwe doorbraak zou de grenzen van de miniaturisering van elektronische componenten verder kunnen verleggen dan eerder voor mogelijk werd gehouden. Een team van het Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) en het Institut d'Électronique, de Microélectronique et de Nanotechnologie (IEMN) heeft een nanometrische transistor gebouwd die uitzonderlijke eigenschappen vertoont voor een apparaat van zijn formaat. Om dit resultaat te bereiken, de onderzoekers ontwikkelden een nieuwe driedimensionale architectuur bestaande uit een verticale nanodraadarray waarvan de geleidbaarheid wordt geregeld door een poort van slechts 14 nm lang.

Gepubliceerd in nanoschaal , deze bevindingen openen de weg naar alternatieven voor de vlakke structuren die worden gebruikt in microprocessors en geheugeneenheden. Het gebruik van 3D-transistors zou het vermogen van micro-elektronische apparaten aanzienlijk kunnen vergroten.

De "bouwstenen" van micro-elektronica, transistors bestaan uit een halfgeleidercomponent, kanaal genoemd, het koppelen van twee terminals. De stroom van stroom tussen deze terminals wordt geregeld door een derde terminal, poort genoemd. Gedraagt zich als een schakelaar, de gate bepaalt of de transistor aan of uit staat. In de afgelopen 50 jaar is transistors zijn gestaag verkleind, waardoor de ontwikkeling van steeds krachtigere micro-elektronische apparaten mogelijk wordt. Echter, men is het er algemeen over eens dat de hedendaagse transistors, met hun vlakke architectuur, naderen de grenzen van de miniaturisering:er is een minimumgrootte waaronder de poortcontrole over het kanaal steeds minder effectief wordt. Vooral, lekstromen beginnen te interfereren met de logische bewerkingen die door de transistorarray worden uitgevoerd. Om dit probleem op te lossen, onderzoekers over de hele wereld onderzoeken alternatieven waarmee de race naar miniaturisatie kan doorgaan.

Een team van onderzoekers van LAAS en IEMN heeft nu de eerste echt driedimensionale nanometrische transistor gebouwd. Het apparaat bestaat uit een strakke verticale nanodraadreeks van ongeveer 200 nm lang die twee geleidende oppervlakken met elkaar verbindt. Een chroompoort omringt elke nanodraad volledig en regelt de stroomstroom, resulterend in een optimale transistorregeling voor een systeem van deze omvang. De poort is slechts 14 nm lang, vergeleken met 28 nm voor de transistors in de huidige chips, maar het vermogen om de stroom in het kanaal van de transistor te regelen voldoet aan de eisen van de hedendaagse micro-elektronica.

Deze architectuur zou kunnen leiden tot de ontwikkeling van microprocessors waarin de transistors op elkaar worden gestapeld. Het aantal transistoren in een bepaalde ruimte zou dus aanzienlijk kunnen worden vergroot, samen met de prestatiecapaciteit van microprocessors en geheugeneenheden. Een ander belangrijk voordeel van deze componenten is dat ze relatief eenvoudig te vervaardigen zijn en geen lithografie met hoge resolutie vereisen. In aanvulling, deze 3D-transistors kunnen gemakkelijk worden geïntegreerd in de conventionele micro-elektronische apparaten die tegenwoordig door de industrie worden gebruikt.

Op deze transistors is patent aangevraagd. De onderzoekers zijn nu van plan hun inspanningen voort te zetten om de poort verder te verkleinen, waarvan ze denken dat ze kleiner dan 10 nm kunnen worden gemaakt, terwijl ze nog steeds een bevredigende controle over de transistor bieden. In aanvulling, het team is op zoek naar industriële partners om de elektronische apparaten van de toekomst te helpen ontwerpen met behulp van de 3D-architectuur van deze nieuwe transistors.

Onderzoekers gebruiken de natuur om kogelvrije coatings te maken

Onderzoekers gebruiken de natuur om kogelvrije coatings te maken Een nieuwe gelelektroforesetechniek voor snelle biomarkerdiagnose via massaspectrometrie

Een nieuwe gelelektroforesetechniek voor snelle biomarkerdiagnose via massaspectrometrie Batterijprestaties beoordelen:in vergelijking met wat?

Batterijprestaties beoordelen:in vergelijking met wat? Nieuwe methode om het duurzaamheidsprobleem van plastic op te lossen

Nieuwe methode om het duurzaamheidsprobleem van plastic op te lossen Experiment voor het plaatsen van een ei in azijn

Experiment voor het plaatsen van een ei in azijn

Brandwerend tropisch woud op de rand van verdwijning

Brandwerend tropisch woud op de rand van verdwijning Welke elementen make-up de atmosfeer van de aarde?

Welke elementen make-up de atmosfeer van de aarde?  Insecten en bloemen in savannegras

Insecten en bloemen in savannegras  Aardwetenschappers roepen op tot preventie- en waarschuwingssystemen voor overstromingen in de Himalaya

Aardwetenschappers roepen op tot preventie- en waarschuwingssystemen voor overstromingen in de Himalaya Uitzonderlijk veel wintersneeuw op noordelijk halfrond dit jaar

Uitzonderlijk veel wintersneeuw op noordelijk halfrond dit jaar

Hoofdlijnen

- Franse regering verklaart de oorlog aan pesticiden

- Wetenschappers visualiseren de structuur van de belangrijkste DNA-reparatiecomponent met een bijna-atomaire resolutie

- De dichtheid van de Wolbachia-bacterie verandert per seizoen bij vlinders

- Hoeveel steenarenden zijn er?

- CRISPR-octrooioorlogen benadrukken het probleem van het verlenen van brede intellectuele eigendomsrechten voor technologie die publieke voordelen biedt

- Kaketoes matchen objecten in corresponderende frames in een taak met gereedschap

- Kevers felle kleuren gebruikt voor camouflage in plaats van roofdieren te waarschuwen

- Wat is een gen?

- Verkoudheidsvirussen onthullen een van hun sterke punten

- Studie draagt bij aan de productie van flexibele elektronische apparaten

- Team creëert nieuwe technologie voor complexe microstructuren voor gebruik in sensoren, andere apps

- Een krachtige techniek om celbewegingen en signalering in vivo te observeren

- Mechanisch geactiveerd ionentransport over koolstofnanobuisjes met één cijfer

- Team maakt met de hand korte nanobuisjes om de productietijd drastisch te verkorten

Wat betekent het om cisgender te zijn?

Wat betekent het om cisgender te zijn? Dankzij de techniek voor het bewerken van genen kunnen zijderupsen spinnenzijde produceren

Dankzij de techniek voor het bewerken van genen kunnen zijderupsen spinnenzijde produceren ALMA legt prachtige uitkomst vast van stellaire strijd

ALMA legt prachtige uitkomst vast van stellaire strijd Een derde van de wereldwijde landbouwgrond met een hoog risico op vervuiling door pesticiden

Een derde van de wereldwijde landbouwgrond met een hoog risico op vervuiling door pesticiden Haploid versus Diploid: wat zijn de overeenkomsten en verschillen?

Haploid versus Diploid: wat zijn de overeenkomsten en verschillen?  Wat is het decibelniveau van een straalvliegtuig?

Wat is het decibelniveau van een straalvliegtuig?  Koolstof nanocomposieten zijn nu een stap dichter bij praktische industriële

Koolstof nanocomposieten zijn nu een stap dichter bij praktische industriële Definitie van Tertiaire consument

Definitie van Tertiaire consument

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | German | Dutch | Danish | Norway | Swedish |

-

Wetenschap © https://nl.scienceaq.com