Wetenschap

Logisch apparaat met koolstofnanobuisjes werkt op subnanowattvermogen

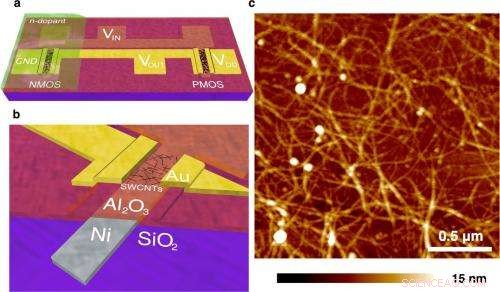

Illustraties van (a) de CNT CMOS-omvormer en (b) een doorsnede van een individuele CNT-transistor, inclusief een 25 nm dikke Ni-poort die een ultralaag stroomverbruik mogelijk maakt. (c) Atoomkrachtmicroscopiebeeld van de CNT-filmmorfologie in het transistorkanaalgebied. Krediet:Geier, et al. ©2013 American Chemical Society

(Phys.org) —Onderzoekers hebben een nieuw op koolstof nanobuisjes (CNT) gebaseerd logisch apparaat gedemonstreerd dat slechts 0,1 nanowatt (nW) verbruikt in de statische AAN- en UIT-toestanden, vertegenwoordigt de laagste gerapporteerde waarde met 3 ordes van grootte voor op CNT gebaseerde CMOS-logische apparaten. Het apparaat zou kunnen dienen als bouwsteen voor grote oppervlakten, ultralow-power CNT logische circuits die kunnen worden gebruikt om een verscheidenheid aan nano-elektronica-toepassingen te realiseren.

De onderzoekers, Michael L. Geier, et al., aan de Northwestern University in Evanston, Illinois, en de Universiteit van Minnesota in Minneapolis, hebben hun paper over de subnanowatt CNT-logica gepubliceerd in een recent nummer van Nano-letters .

"Een moderne geïntegreerde schakeling heeft meer dan 1 miljard transistors, " co-auteur Mark C. Hersam, Hoogleraar Materiaalkunde en Engineering, Scheikunde, en geneeskunde aan de Northwestern University, vertelde Phys.org . "Bijgevolg, de vermogensdissipatie per transistor moet zeer laag zijn om de gehele schakeling een redelijk stroomverbruik te laten hebben. In feite, algemeen wordt aangenomen dat het stroomverbruik de belangrijkste beperkende factor is voor het bereiken van verdere toename van de complexiteit (d.w.z. aantal transistors) in geïntegreerde schakelingen."

Zoals de onderzoekers uitleggen, een van de grootste voordelen van CMOS-architectuur is dat het een intrinsiek laag stroomverbruik heeft. Dit voordeel vloeit voort uit het feit dat, in tegenstelling tot andere logische architecturen, een van de twee typen transistors (p-type of n-type) wordt uitgeschakeld onder stabiele omstandigheden in elke logische poort in CMOS-apparaten.

Om dit potentieel voor een extreem laag stroomverbruik volledig te benutten, de p-type en n-type transistoren moeten nauwkeurig afgestemde en goed gescheiden drempelspanningen hebben, dat zijn de spanningsniveaus die bepalen of het apparaat AAN of UIT is. Tot dusver, dit probleem van de drempelspanningen is niet aangepakt, en de onderzoekers hier identificeerden het als de belangrijkste uitdaging die de realisatie van sterk geïntegreerde CNT-gebaseerde CMOS-elektronica beperkt.

In hun studie hebben de onderzoekers gebruikten een metalen poortstructuur om symmetrische en duidelijk gescheiden drempelspanningen te bereiken voor p-type en n-type CNT-transistoren, wat resulteert in het ultralage stroomverbruik. In de statische toestanden, waarin het apparaat AAN of UIT staat, stroomverbruik is minder dan 0,1 nW. In het midden van de overdrachtstoestand, wanneer zowel p-type als n-type transistors tegelijkertijd in de AAN-status zijn, de spanning bereikt zijn piek bij 10 nW.

Door meerdere CNT-transistoren in verschillende configuraties aan te sluiten, de onderzoekers demonstreerden omvormer, NAND en NOR logische poorten. In de toekomst, deze poorten kunnen worden geïntegreerd in complexe circuits, waar ze een statisch stroomverbruik van subnanowatt kunnen bieden, samen met de andere voordelen van CNT's, zoals oplossingsverwerkbaarheid en flexibiliteit.

"We werken nu aan het maken van meer gecompliceerde circuits, waar we substantieel meer transistors en gecascadeerde logische poorten zullen hebben, "Zei Hersam. "We hebben ook interesse in het combineren van koolstofnanobuisjes met andere opkomende nano-elektronische materialen in ons laboratorium (bijv. molybdeendisulfide [MoS 2 ])."

© 2013 Fysio.org. Alle rechten voorbehouden.

Een veelzijdige, geïntegreerde workflow voor interactie proteomics

Een veelzijdige, geïntegreerde workflow voor interactie proteomics Nieuwe textielcoating kan chemische wapens dwarsbomen, Red levens

Nieuwe textielcoating kan chemische wapens dwarsbomen, Red levens Apparaat verandert schelpen van zeedieren in kracht voor medische, augmented reality, mobiele apparaten

Apparaat verandert schelpen van zeedieren in kracht voor medische, augmented reality, mobiele apparaten Geen superbugs meer? Ahornsiroopextract verbetert de antibiotische werking

Geen superbugs meer? Ahornsiroopextract verbetert de antibiotische werking Neutronen ontsluiten eigenschappen van nieuw poreus metaalhydride voor mogelijke nieuwe toepassingen voor energieopslag

Neutronen ontsluiten eigenschappen van nieuw poreus metaalhydride voor mogelijke nieuwe toepassingen voor energieopslag

Hoofdlijnen

- Lichtgroene planten besparen stikstof zonder in te boeten aan fotosynthetische efficiëntie

- Galapagos-studie toont aan dat nieuwe soorten zich in slechts twee generaties kunnen ontwikkelen

- Het verschil tussen anafase, interfase, metafase en profase

- Stresstest:uit nieuwe studie blijkt dat zeehonden gestrest zijn door haaien

- De effecten van algen in drinkwater

- Wetenschap komt dichter bij het verklaren van de boze dronkaard

- Je kunt echt op je naam lijken,

- Hoe empathie werkt

- Studie belicht botanische vooroordelen

- Flexibele koolstofnanobuiscircuits betrouwbaarder gemaakt, energiezuinig

- Wetenschappers vinden techniek om superroosters van koolstof voor elektronische kwantumapparaten te verbeteren

- De nanotechnologie van zonnedauw en Engelse klimop

- Nieuwe nanotech-uitvinding verbetert de effectiviteit van de penicilline van kanker

- Een nieuw cellulair proces om materialen van nanoformaat te verzwelgen

Thuiswerken maakt ons productiever en innovatiever, zegt enquête

Thuiswerken maakt ons productiever en innovatiever, zegt enquête Amazon stopt bouwproject in Seattle voorafgaand aan belastingstemming

Amazon stopt bouwproject in Seattle voorafgaand aan belastingstemming Naast Otzi the Iceman:een overvloed aan oeroude mossen en levermossen

Naast Otzi the Iceman:een overvloed aan oeroude mossen en levermossen Nanopore opent nieuwe cellulaire doorgang voor drugstransport

Nanopore opent nieuwe cellulaire doorgang voor drugstransport Argonne-ontdekking biedt nieuwe manier om nucleair materiaal te coaten

Argonne-ontdekking biedt nieuwe manier om nucleair materiaal te coaten ADB zegt dat Azië de uitgaven voor infrastructuur moet verdubbelen

ADB zegt dat Azië de uitgaven voor infrastructuur moet verdubbelen Wetenschapsprojecten die gebruikmaken van M & M; s

Wetenschapsprojecten die gebruikmaken van M & M; s  Noorwegen ziet olie in zijn toekomst ondanks waarschuwingen

Noorwegen ziet olie in zijn toekomst ondanks waarschuwingen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Portuguese | Swedish | German | Dutch | Danish | Norway | Spanish |

-

Wetenschap © https://nl.scienceaq.com