Wetenschap

Universele transistor dient als basis om elke logische functie uit te voeren

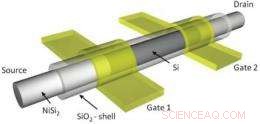

De kern van de herconfigureerbare transistor bestaat uit een nanodraadstructuur die is ingebed in een siliciumdioxide-omhulsel. Elektronen of gaten stromen van de bron aan het ene uiteinde van de nanodraad door twee poorten naar de afvoer aan het andere uiteinde van de nanodraad. Eén poort wordt gebruikt om de p- of n-polariteit te programmeren, terwijl de andere poort de geleiding door de nanodraad afstemt. Afbeelding tegoed:©Namlab gGmbH

(PhysOrg.com) -- De meeste hedendaagse elektronische apparaten bevatten twee verschillende soorten veldeffecttransistoren (FET's):n-type (die elektronen gebruiken als ladingsdrager) en p-type (die gaten gebruiken). Over het algemeen, een transistor kan maar van het ene of het andere type zijn, maar niet allebei. Nu in een nieuwe studie, onderzoekers hebben een transistor ontworpen die zichzelf kan herconfigureren als n-type of p-type wanneer geprogrammeerd door een elektrisch signaal. Een set van deze "universele transistors" kan, in principe, elke Booleaanse logische bewerking uitvoeren, wat betekent dat circuits hetzelfde aantal logische functies kunnen uitvoeren met minder transistors. Dit voordeel zou kunnen leiden tot compactere hardware en nieuwe circuitontwerpen.

De onderzoekers die de transistor hebben ontworpen, geleid door Walter M. Weber bij Namlab gGmbH in Dresden, Duitsland, hebben het nieuwe concept gepubliceerd in een recent nummer van Nano-letters .

“Synthetische nanodraden worden gebruikt om het proof-of-principle te realiseren, Weber vertelde PhysOrg.com . "Echter, het concept is volledig overdraagbaar naar state-of-the-art CMOS-siliciumtechnologie en kan gebruik maken van zelf-uitgelijnde processen.”

De kern van de nieuwe transistor bestaat uit een enkele nanodraad gemaakt van een metaal-halfgeleider-metaalstructuur, die is ingebed in een siliciumdioxide-omhulsel. Elektronen of gaten stromen van de bron aan het ene uiteinde van de nanodraad door twee poorten naar de afvoer aan het andere uiteinde van de nanodraad. De twee poorten regelen de stroom van elektronen of gaten op verschillende manieren. Eén poort selecteert het transistortype door ervoor te kiezen elektronen of gaten te gebruiken, terwijl de andere poort de elektronen of gaten regelt door de geleiding van de nanodraad af te stemmen.

Het gebruik van een poort om een p- of n-type configuratie te selecteren is heel anders dan bij conventionele transistors. In conventionele transistoren, p- of n-type operatie resultaten van doping die optreedt tijdens het fabricageproces, en kan niet worden gewijzigd zodra de transistor is gemaakt. In tegenstelling tot, de herconfigureerbare transistor gebruikt geen doping. In plaats daarvan, een externe spanning die op één poort wordt toegepast, kan het transistortype zelfs tijdens bedrijf opnieuw configureren. De spanning zorgt ervoor dat de Schottky-overgang nabij de poort de stromen van elektronen of gaten door het apparaat blokkeert. Dus als elektronen worden geblokkeerd, gaten kunnen stromen en de transistor is van het p-type. Door een iets andere spanning aan te leggen, de herconfiguratie kan weer worden geschakeld, zonder de stroming te verstoren.

De wetenschappers leggen uit dat de sleutel om deze herconfiguratie te laten werken, de mogelijkheid is om het elektronische transport over elk van de twee knooppunten (één per poort) afzonderlijk af te stemmen. Hun simulaties toonden aan dat de stroom wordt gedomineerd door tunneling, wat suggereert dat de nanodraadgeometrie een belangrijke rol speelt bij het vermogen tot onafhankelijke junctiecontrole.

Omdat de herconfigureerbare transistor de logische functies van zowel p- als n-type FET's kan uitvoeren, een enkele transistor kan zowel een p- als n-type FET in een circuit vervangen, wat de grootte van het circuit aanzienlijk zou verminderen zonder de functionaliteit te verminderen. Zelfs in dit vroege stadium de herconfigureerbare transistor vertoont zeer goede elektrische eigenschappen, inclusief een record aan/uit-verhouding en verminderde lekstroom in vergelijking met conventionele nanodraad-FET's. In de toekomst, de onderzoekers zijn van plan om de prestaties van de transistor verder te verbeteren.

"We variëren de materiaalcombinaties om de prestaties van het apparaat verder te verbeteren, ' zei Weber. "Verder, de eerste circuits die deze apparaten implementeren, worden gebouwd. … De grootste uitdaging zal zijn om de extra gate-signalen in de cellay-out op te nemen, waardoor flexibele interconnectie met de andere transistoren mogelijk wordt.”

Copyright 2011 PhysOrg.com.

Alle rechten voorbehouden. Dit materiaal mag niet worden gepubliceerd, uitzending, geheel of gedeeltelijk herschreven of herverdeeld zonder de uitdrukkelijke schriftelijke toestemming van PhysOrg.com.

Katalytische hydrogenering van kooldioxide tot methanol

Katalytische hydrogenering van kooldioxide tot methanol Induced-fit adsorbens voor acetyleen

Induced-fit adsorbens voor acetyleen Nieuwe materialen met een hoge zuurstof-ionengeleiding die een duurzame toekomst opent

Nieuwe materialen met een hoge zuurstof-ionengeleiding die een duurzame toekomst opent Ingenieurs vinden een nette manier om afvalkooldioxide om te zetten in bruikbaar materiaal

Ingenieurs vinden een nette manier om afvalkooldioxide om te zetten in bruikbaar materiaal Chemici ontdekken manier om nieuwe stikstofproducten uit het niets te maken

Chemici ontdekken manier om nieuwe stikstofproducten uit het niets te maken

Diepduikende wetenschappers zeggen dat ondiepe riffen niet kunnen vertrouwen op schemerzonesystemen voor herstel

Diepduikende wetenschappers zeggen dat ondiepe riffen niet kunnen vertrouwen op schemerzonesystemen voor herstel Microklimaten in steden en aan de kust voorspellen

Microklimaten in steden en aan de kust voorspellen Voor een betere toekomst, gebruik deze tijd om thuis groene gewoontes aan te leren

Voor een betere toekomst, gebruik deze tijd om thuis groene gewoontes aan te leren Oppervlaktemeren zorgen ervoor dat Antarctische ijsplaten buigen

Oppervlaktemeren zorgen ervoor dat Antarctische ijsplaten buigen Warmte, vochtigheid houdt het oosten van de VS vast terwijl het weekend ploetert

Warmte, vochtigheid houdt het oosten van de VS vast terwijl het weekend ploetert

Hoofdlijnen

- Een verticale laminaire luchtstromingskap reinigen

- Hoe Cytoplasma voor een celproject te maken

- Wat is het doel van ademhaling?

- Lantaarnvissen onthullen hoe de opwarming van de oceaan de schemerzone beïnvloedt

- "What is Pascals Triangle?

- De machtige Banyan-boom kan eeuwenlang lopen en leven

- Ethiek Research Paper Onderwerpen

- Gebruik je echt maar 10 procent van je hersenen?

- Verschil tussen bacteriële en plantencelwand

- Ontwikkeling van DNA-val maakt de weg vrij voor gepersonaliseerde geneeskunde

- Biofotonica-methode kan leiden tot identificatie van onstabiele plaques

- DNA-origami beschermen voor de toediening van geneesmiddelen tegen kanker

- Supergeleidende krachten van grafenen ontgrendelen met een draai en een kneepje

- Project zal reactiekinetiekgegevens opleveren voor deterministische synthese van metalen nanokristallen

Nieuwe biologische steiger biedt veelbelovende basis voor gemanipuleerde weefsels

Nieuwe biologische steiger biedt veelbelovende basis voor gemanipuleerde weefsels Een demografisch percentage berekenen

Een demografisch percentage berekenen  De dubbel magische kern van lood-208 - het draait, hoewel het niet zou moeten

De dubbel magische kern van lood-208 - het draait, hoewel het niet zou moeten Hoe Facebook-advertenties u targeten

Hoe Facebook-advertenties u targeten Nieuwe terahertz-beeldvormingsbenadering kan de detectie van huidkanker versnellen

Nieuwe terahertz-beeldvormingsbenadering kan de detectie van huidkanker versnellen Multimeteronderdelen & functies

Multimeteronderdelen & functies  Werkt de vijf seconden regel echt?

Werkt de vijf seconden regel echt?  Een hotspot in een koude plek veranderen:Fano-vormige lokale veldreacties onderzocht door een kwantumpunt

Een hotspot in een koude plek veranderen:Fano-vormige lokale veldreacties onderzocht door een kwantumpunt

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Swedish | German | Dutch | Danish | Norway | Portuguese |

-

Wetenschap © https://nl.scienceaq.com