Wetenschap

Onderzoeksalliantie bouwt nieuwe transistor voor 5nm-technologie

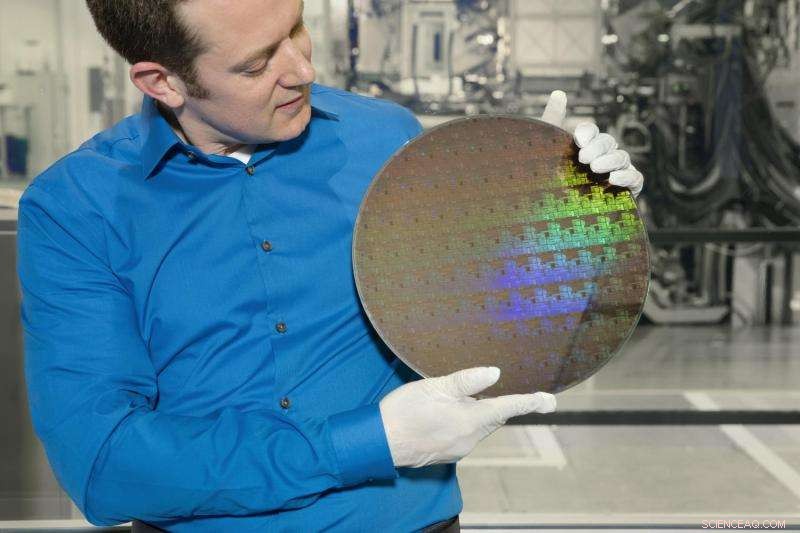

IBM Research-wetenschapper Nicolas Loubet heeft een wafeltje chips met 5nm silicium nanosheet-transistors die zijn vervaardigd met behulp van een in de industrie uniek proces dat een prestatieverbetering van 40 procent kan leveren bij vast vermogen, of 75 procent energiebesparing bij gelijke prestaties. Krediet:Connie Zhou

IBM, haar Research Alliance-partners Globalfoundries en Samsung, en leveranciers van apparatuur hebben een proces ontwikkeld dat voor het eerst in de branche is gebruikt om silicium nanosheet-transistors te bouwen die 5 nanometer (nm)-chips mogelijk maken. De details van het proces zullen worden gepresenteerd op de 2017 Symposia on VLSI Technology and Circuits-conferentie in Kyoto, Japan. In minder dan twee jaar sinds de ontwikkeling van een 7nm-testknooppuntchip met 20 miljard transistors, wetenschappers hebben de weg vrijgemaakt voor 30 miljard schakelaars op een chip ter grootte van een vingernagel.

De resulterende prestatieverbetering zal cognitief computergebruik helpen versnellen, het internet der dingen (IoT), en andere data-intensieve applicaties die in de cloud worden geleverd. De energiebesparing zou ook kunnen betekenen dat de batterijen in smartphones en andere mobiele producten twee tot drie keer langer meegaan dan de huidige apparaten, voordat deze moet worden opgeladen.

Wetenschappers die werken als onderdeel van de door IBM geleide Research Alliance aan het SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex in Albany, NY bereikte de doorbraak door stapels silicium nanosheets te gebruiken als de apparaatstructuur van de transistor, in plaats van de standaard FinFET-architectuur, dat is de blauwdruk voor de halfgeleiderindustrie tot 7nm-knooppunttechnologie.

"Om het bedrijfsleven en de samenleving de komende jaren te laten voldoen aan de eisen van cognitieve en cloudcomputing, vooruitgang in de halfgeleidertechnologie is essentieel, " zei Arvind Krishna, senior Vice President, hybride cloud, en directeur, IBM-onderzoek. "Daarom streeft IBM agressief naar nieuwe en andere architecturen en materialen die de grenzen van deze industrie verleggen, en brengt ze op de markt in technologieën zoals mainframes en onze cognitieve systemen."

IBM-wetenschappers van het SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex in Albany, NY bereidt testwafels voor met 5nm silicium nanosheet-transistors, geladen in de verenigde pod aan de voorkant, of FOUP's, om een in de industrie uniek proces te testen voor het bouwen van 5nm-transistors met behulp van silicium nanosheets. Krediet:Connie Zhou

De demonstratie van silicium nanosheettransistors, zoals beschreven in de Research Alliance paper Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET, en uitgegeven door VLSI, bewijst dat 5nm-chips mogelijk zijn, krachtiger, en niet te ver weg in de toekomst.

Vergeleken met de toonaangevende 10nm-technologie die op de markt verkrijgbaar is, een op nanosheets gebaseerde 5nm-technologie kan 40 procent prestatieverbetering leveren bij vast vermogen, of 75 procent energiebesparing bij gelijke prestaties. Deze verbetering zorgt voor een aanzienlijke boost om te voldoen aan de toekomstige eisen van kunstmatige intelligentie (AI)-systemen, virtual reality en mobiele apparaten.

Een nieuwe schakelaar bouwen

"Deze aankondiging is het nieuwste voorbeeld van het onderzoek van wereldklasse dat voortkomt uit onze baanbrekende publiek-private samenwerking in New York, " zei Gary Patton, CTO en Head of Worldwide R&D bij Globalfoundries. "Terwijl we vooruitgang boeken in de richting van de commercialisering van 7nm in 2018 in onze Fab 8-productiefaciliteit, we streven actief naar de volgende generatie technologieën op 5nm en daarbuiten om technologisch leiderschap te behouden en onze klanten in staat te stellen een kleinere, sneller, en meer kostenefficiënte opwekking van halfgeleiders."

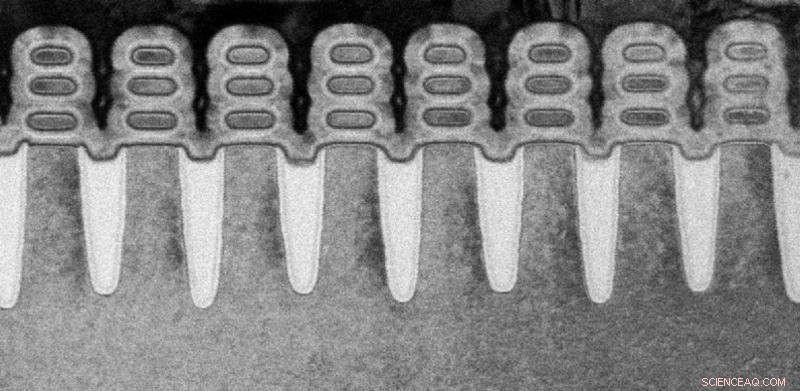

Afgebeeld:een scan van de 5nm-transistor van IBM Research Alliance, gebouwd met behulp van een in de industrie uniek proces om silicium nanosheets te stapelen als de apparaatstructuur - het bereiken van een schaal van 30 miljard schakelaars op een chip ter grootte van een vingernagel die aanzienlijke vermogens- en prestatieverbeteringen zal leveren ten opzichte van de huidige state-of-the-art 10nm-chips. Krediet:IBM

IBM Research onderzoekt al meer dan 10 jaar nanosheet-halfgeleidertechnologie. Dit werk is het eerste in de industrie dat de haalbaarheid aantoont om gestapelde nanosheet-apparaten te ontwerpen en te fabriceren met elektrische eigenschappen die superieur zijn aan de FinFET-architectuur.

Dezelfde Extreme Ultraviolet (EUV) lithografie-aanpak die werd gebruikt om het 7nm-testknooppunt en de 20 miljard transistors te produceren, werd toegepast op de nanosheet-transistorarchitectuur. Met behulp van EUV-lithografie, de breedte van de nanosheets kan traploos worden aangepast, allemaal binnen één productieproces of chipontwerp. Deze aanpasbaarheid maakt het mogelijk de prestaties en het vermogen voor specifieke circuits te verfijnen - iets wat niet mogelijk is met de huidige FinFET-transistorarchitectuurproductie, die wordt beperkt door de stroomvoerende vinhoogte. Daarom, terwijl FinFET-chips kunnen schalen tot 5nm, het simpelweg verkleinen van de ruimte tussen de vinnen zorgt niet voor meer stroom voor extra prestaties.

"De aankondiging van vandaag zet de publiek-private modelsamenwerking met IBM voort die SUNY-Polytechnic's energie geeft, Albany's, en het leiderschap en de innovatie van de staat New York bij het ontwikkelen van technologieën van de volgende generatie, " zei dr. Bahgat Sammakia, interim-voorzitter, SUNY Polytechnisch Instituut. "Wij zijn van mening dat het inschakelen van de eerste 5nm-transistor een belangrijke mijlpaal is voor de hele halfgeleiderindustrie, aangezien we verder gaan dan de beperkingen van onze huidige mogelijkheden. De samenwerking van SUNY Poly met IBM en Empire State Development is een perfect voorbeeld van hoe de industrie, Overheid en wetenschap kunnen succesvol samenwerken en een brede en positieve impact hebben op de samenleving."

Een deel van IBM's $ 3 miljard, vijfjarige investering in chip-R&D (aangekondigd in 2014), het bewijs van de schaalbaarheid van nanosheet-architectuur naar een 5nm-knooppunt zet IBM's erfenis van historische bijdragen aan silicium- en halfgeleiderinnovatie voort. Ze omvatten de uitvinding of eerste implementatie van de single cell DRAM, de Dennard-schaalwetten, chemisch versterkte fotoresists, koper verbindt bedrading, Silicium op Isolator, gespannen techniek, multi-core microprocessors, immersie lithografie, hoge snelheid SiGe, High-k gate diëlektrica, ingebed DRAM, 3D-chipstapeling en luchtspleetisolatoren.

De oorzaak van capaciteitsverlies vinden in een metaaloxide batterijmateriaal

De oorzaak van capaciteitsverlies vinden in een metaaloxide batterijmateriaal Wat is het verschil tussen elektronische geometrie en moleculaire vorm?

Wat is het verschil tussen elektronische geometrie en moleculaire vorm?  De fundamentele chemie achter elektrokatalytische watersplitsing

De fundamentele chemie achter elektrokatalytische watersplitsing DNA-nanostructuren worden gecamoufleerd door eiwitten

DNA-nanostructuren worden gecamoufleerd door eiwitten Test bepaalt personen die waarschijnlijk DNA afstaan op plaats delict

Test bepaalt personen die waarschijnlijk DNA afstaan op plaats delict

In droge Antarctische valleien, vroege tekenen van door klimaatverandering veroorzaakte verschuivingen in de bodem

In droge Antarctische valleien, vroege tekenen van door klimaatverandering veroorzaakte verschuivingen in de bodem Wat is de meest overvloedige organische verbinding op aarde?

Wat is de meest overvloedige organische verbinding op aarde?  Hoe beïnvloedt luchtmassa het klimaat?

Hoe beïnvloedt luchtmassa het klimaat?

Een luchtmassa is een grote eenheid van de lagere atmosfeer die wordt gedefinieerd door gemeenschappelijke fysieke kenmerken, zoals temperatuur en vochtigheid, op elke gegeven hoogte en een die onopvallend en

Het noordpoolgebied is in 3 miljoen jaar niet zo warm geweest – en dat voorspelt grote veranderingen voor de rest van de planeet

Het noordpoolgebied is in 3 miljoen jaar niet zo warm geweest – en dat voorspelt grote veranderingen voor de rest van de planeet Hoe een Paper Hornets Nest

Hoe een Paper Hornets Nest

Hoofdlijnen

- Welke effecten kunnen glycolyse remmen?

- Hoe beïnvloedt fosforylatie eiwitactiviteit?

- Klonten als tijdelijke opslag

- De functie van macromoleculen

- Vertrouwen op GPS voorkomt dat delen van uw hersenen worden geactiveerd

- Zeven nieuwe spinnensoorten uit Brazilië vernoemd naar zeven beroemde fictieve spinnenpersonages

- Onderzoekstopics in Biotechnology

- Het bewijs zit in de voetafdruk:mensen kwamen eerder naar Amerika dan gedacht

- Kill-schakelaars voor gemanipuleerde microben die schurkenstaten zijn geworden

- Grafeen in nul G belooft succes in de ruimte

- Nieuwe manieren ontwerpen om materiaal te begrijpen

- Onderzoekers combineren met succes twee verschillende materialen om nieuw hyperefficiënt lichtgevend kristal te creëren

- In nanodiamanten ingebedde contactlenzen kunnen de behandeling van glaucoom verbeteren

- Lok-nanodeeltjes kunnen hiv blokkeren en infectie voorkomen

Een moreel kompas ontwikkelen op basis van menselijke teksten

Een moreel kompas ontwikkelen op basis van menselijke teksten Nieuw model voorspelt de verspreiding van COVID-19 - en hoe financiële en economische risico's te beheersen

Nieuw model voorspelt de verspreiding van COVID-19 - en hoe financiële en economische risico's te beheersen Satellietinformatie gebruiken om na een ramp opnieuw op te bouwen

Satellietinformatie gebruiken om na een ramp opnieuw op te bouwen Bemanningen in Zuid-Spanje worden voor 5e dag geconfronteerd met complexe bosbranden

Bemanningen in Zuid-Spanje worden voor 5e dag geconfronteerd met complexe bosbranden Jonge mannen over sexting:het is normaal, maar ingewikkeld

Jonge mannen over sexting:het is normaal, maar ingewikkeld Oceaancirculatie is de sleutel tot het begrijpen van onzekerheden in voorspellingen van klimaatverandering

Oceaancirculatie is de sleutel tot het begrijpen van onzekerheden in voorspellingen van klimaatverandering Het is echt anders voor jonge mensen:het is moeilijker om de banenladder te beklimmen

Het is echt anders voor jonge mensen:het is moeilijker om de banenladder te beklimmen NASA ziet tropische storm Irwin bewegen in de post-tropische storm Hilarys kielzog

NASA ziet tropische storm Irwin bewegen in de post-tropische storm Hilarys kielzog

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com