Wetenschap

GPU-nieuws:tijd voor een nieuwe poging op een waferscale-computer

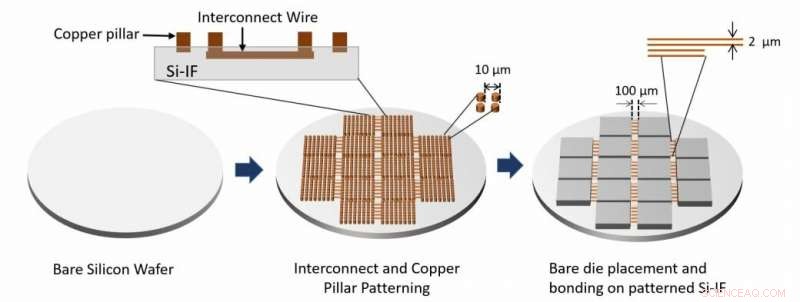

De processtroom van de systeemassemblage wordt weergegeven. Interconnect-lagen en koperen pilaren worden gemaakt door de kale siliciumwafel te verwerken. Kale matrijzen worden vervolgens met TCB op de wafer gelijmd. Credit:Waferscale-processors ontwerpen - een GPU-casestudy, HPCA 19.

Onderzoekers van de Universiteit van Illinois in Urbana-Champaign en de Universiteit van Californië, Los Angeles, achter de recente ontwikkeling voor een computer op waferschaal die sneller, energiezuiniger, dan hedendaagse tegenhangers.

Ingenieurs streven ernaar om iets genaamd "silicium interconnect fabric" te gebruiken om een computer te bouwen met 40 GPU's op een enkele siliciumwafer. TechSpot en andere sites berichtten over hun werk en hun paper, deze maand te presenteren.

Wat achtergrondinformatie over Si-IF:"In de afgelopen twee decennia hebben siliciumchips zijn 1000x kleiner geworden, terwijl pakketten op printplaten slechts 4x zijn gekrompen, " zei UCLA Technology Development Group. Een oplossing is "silicium interconnect fabric (Si-IF)."

Samuel Moore bij IEEE-spectrum heeft een veel geciteerd artikel over het onderwerp waarin hij resultaten opmerkte:"Simulaties van dit monster met meerdere processors versnelden berekeningen bijna 19-voudig en verminderden de combinatie van energieverbruik en signaalvertraging meer dan 140-voudig."

Namelijk, de onderzoeksinspanning is onder leden van de afdeling elektrotechniek en computertechniek, Universiteit van Californië, Los Angeles, en afdeling elektrotechniek en computertechniek, Universiteit van Illinois in Urbana-Champaign. Hun paper is getiteld "Architecting Waferscale Processors-A GPU Case Study."

lllinois universitair hoofddocent computertechniek Rakesh Kumar en zijn collega's zijn al begonnen met het bouwen van een prototype-processorsysteem op waferschaal. De groep zal het verder onderzoeken om inzicht te krijgen in eventuele problemen die zich kunnen voordoen. Ze geloofden dat de tijd rijp was om waferscale-architecturen opnieuw te bekijken.

Mark Tyson in Hexus :"Ingenieurs aan de University of Illinois Urbana-Champaign en aan de University of California Los Angeles denken dat het tijd is voor een nieuwe poging om een computer op waferschaal te maken."

Het accent kan op het woord worden gelegd herzien . Het team schreef in hun krant, "Niet verrassend, waferscale-processors werden in de jaren 80 zwaar bestudeerd. Er waren ook verschillende commerciële pogingen om processors op wafelschaal te bouwen. Helaas, ondanks de belofte, dergelijke processors konden geen succes vinden in de mainstream vanwege zorgen over de opbrengst."

Ze zeiden:"hoe groter de processor, hoe lager de opbrengst - de opbrengst op wafelschaal was in die tijd slopend. We stellen dat er sindsdien aanzienlijke vooruitgang is geboekt in de productie- en verpakkingstechnologie en dat het misschien tijd is om de haalbaarheid van waferscale-processors opnieuw te bekijken."

Rakesh Kumar, universitair hoofddocent computertechniek in Illinois, en zijn medewerkers zullen pleiten voor een computer op waferschaal die uit maar liefst 40 GPU's bestaat. De beste kop om ons eraan te herinneren waarom dit interessant is, is te vinden op IEEE-spectrum . "Wat is er beter dan 40 GPU-gebaseerde servers? Een server met 40 GPU's."

Wat is er speciaal:ze hebben standaard GPU-chips die de kwaliteitstests hebben doorstaan - ze creëren een technologie die ze silicon interconnect fabric (SiIF) noemen om ze beter met elkaar te verbinden.

Shawn Knight binnen TechSpot schreef hierover. "Met zo'n nauwe integratie, " zei Ridder, "vanuit het perspectief van de programmeur, het zou eruitzien als één gigantische GPU in plaats van 40 afzonderlijke GPU's."

SiIF vervangt de printplaat door silicium; er is geen chippakket nodig, zei Moore. Hij meldde dat ze in één ontwerp 41 GPU's konden persen. "Ze testten een simulatie van dit ontwerp en ontdekten dat het zowel de berekening als de verplaatsing van gegevens versnelde, terwijl het minder energie verbruikte dan 40 standaard GPU-servers zouden hebben."

Tyson schreef dat "zoals veel HEXUS-lezers zullen weten, meestal verspreiden supercomputers applicaties over honderden GPU's op afzonderlijke PCB's, communiceren via langeafstandsverbindingen. Dergelijke verbindingen zijn traag en energie-inefficiënt in vergelijking met interconnecties binnen de chiparchitectuur." Hij merkte op dat Kumar zei dat het krijgen van gegevens van de ene GPU naar de andere een ongelooflijke hoeveelheid overhead veroorzaakte.

IEEE-spectrum 's Moore legde hun werk in meer detail uit.

"De SiIF-wafer heeft een patroon met een of meer lagen koperen verbindingen van 2 micrometer breed met een onderlinge afstand van slechts 4 micrometer. Dat is vergelijkbaar met het hoogste niveau van verbindingen op een chip. Op de plekken waar de GPU's moeten worden aangesloten , de siliciumwafel is voorzien van een patroon met korte koperen pilaren op een onderlinge afstand van ongeveer 5 micrometer. Daarboven is de GPU uitgelijnd, ingedrukt, en verwarmd. Dit beproefde proces, genaamd thermische compressie bonding, zorgt ervoor dat de koperen pilaren samensmelten met de koperen verbindingen van de GPU. "

Hun werk trok lovende commentaren. Tyson noemde het een moedige maar mogelijk tijdige zet voor de industrie.

Wat is het volgende? Het team zal hun bevindingen presenteren op het IEEE International Symposium on High-Performance Computer Architecture. Het evenement vindt plaats van 16 tot 20 februari in Washington DC.

© 2019 Wetenschap X Netwerk

Een metaalvrije, duurzame benadering van CO2-reductie

Een metaalvrije, duurzame benadering van CO2-reductie Veldproeven tonen aan dat nieuw katalysatormateriaal voor elektrolysers betrouwbaar is

Veldproeven tonen aan dat nieuw katalysatormateriaal voor elektrolysers betrouwbaar is Hoe Amp om te zetten in elektronen per seconde

Hoe Amp om te zetten in elektronen per seconde  Hydrofoob silica-colloïde-elektrolyt is veelbelovend voor veiligere lithium-zuurstofbatterijen

Hydrofoob silica-colloïde-elektrolyt is veelbelovend voor veiligere lithium-zuurstofbatterijen Eenvoudige arseensensor kan levens redden

Eenvoudige arseensensor kan levens redden

Zwarte koolstof en andere vervuilingszaden wolken. We begonnen net de gevolgen voor het klimaat te begrijpen

Zwarte koolstof en andere vervuilingszaden wolken. We begonnen net de gevolgen voor het klimaat te begrijpen Tiny Australia-vogelstalling zaait verdeeldheid in kolenmijnproject

Tiny Australia-vogelstalling zaait verdeeldheid in kolenmijnproject Waarom de wetenschap de geesteswetenschappen nodig heeft om klimaatverandering op te lossen

Waarom de wetenschap de geesteswetenschappen nodig heeft om klimaatverandering op te lossen De hete mantel van de vroege aarde heeft mogelijk geleid tot de Archeïsche waterwereld

De hete mantel van de vroege aarde heeft mogelijk geleid tot de Archeïsche waterwereld Subnationale klimaatclubs kunnen een sleutel zijn tot het bestrijden van klimaatverandering

Subnationale klimaatclubs kunnen een sleutel zijn tot het bestrijden van klimaatverandering

Hoofdlijnen

- Klimaatveranderingen verkorten de mariene voedselketen voor de kust van Californië

- Nieuwe zoomtechniek onthult voor het eerst een elektrisch circuit van cellen

- Microbiële ziekten en mutaties: wat is het ?, Lijsten & Oorzaken

- 4 manieren om te vertellen of gezondheidsrapportage nepnieuws kan zijn

- Ja,

- Wat is de relatie tussen een chromosoom en een allel?

- Westerse steden proberen te voorkomen dat hongerige beren ravage aanrichten

- Twee Caribische vogelvangbomen vernoemd naar twee vrouwen met over het hoofd gezien botanische werken

- Eerste luxe Perigord-truffel wordt in Groot-Brittannië verbouwd

- Volkswagen zet groot in op elektrisch. Kopen consumenten in?

- Facebook werd in 2014 gewaarschuwd voor vermeende Russische inmenging

- Tien van de meest innovatieve robotica-ontwikkelingen van het afgelopen jaar

- Partijdige nieuwsuitzendingen proberen leegte in Amerikaanse nieuwswoestijnen op te vullen

- Geen muzikaal talent, geen probleem, daar zijn nu apps voor

Nieuwe techniek kan beweging van afzonderlijke moleculen gedurende uren detecteren

Nieuwe techniek kan beweging van afzonderlijke moleculen gedurende uren detecteren Ondanks de sociale ontwikkeling, genderattitudes brengen wereldwijd een andere koers in kaart

Ondanks de sociale ontwikkeling, genderattitudes brengen wereldwijd een andere koers in kaart Onderzoekers ontdekken nieuwe manier om elektrische apparaten van stroom te voorzien

Onderzoekers ontdekken nieuwe manier om elektrische apparaten van stroom te voorzien Plastic woestenij:oceaanvervuilingscrisis in Azië

Plastic woestenij:oceaanvervuilingscrisis in Azië De volgende black-out voorkomen

De volgende black-out voorkomen Deepwater Horizon-olie begraven op de stranden van de Golfkust kan tientallen jaren duren om biologisch af te breken

Deepwater Horizon-olie begraven op de stranden van de Golfkust kan tientallen jaren duren om biologisch af te breken Wat hebben de wolkentoppen van Uranuss gemeen met rotte eieren?

Wat hebben de wolkentoppen van Uranuss gemeen met rotte eieren? Wie zou zich bij Apple kunnen aansluiten in de aandelenclub van $ 1 biljoen op Wall Street?

Wie zou zich bij Apple kunnen aansluiten in de aandelenclub van $ 1 biljoen op Wall Street?

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com