Wetenschap

Onderzoekers ontwikkelen schema om naadloze geïntegreerde schakelingen te ontwerpen die op grafeen zijn geëtst

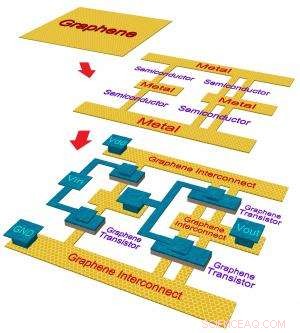

Het bovenste schema is een monolaag grafeenvel. Het middelste schema toont geëtste smalle/brede linten die als halfgeleider/metaal fungeren. Het onderste schema is een circuit dat volledig uit grafeen bestaat na afzetting en patroonvorming van metaal en poortdiëlektricum. Krediet:UCSB Nanoelectronics Research Lab

(Phys.org) —Onderzoekers in elektrische en computertechniek aan de Universiteit van Californië, Santa Barbara heeft een ontwerpschema voor geïntegreerde schakelingen geïntroduceerd en gemodelleerd waarin transistors en interconnects naadloos monolithisch worden gemodelleerd op een vel grafeen, een 2-dimensionaal vlak van koolstofatomen. De demonstratie biedt mogelijkheden voor ultra energiezuinige, flexibel, en transparante elektronica.

Bulkmaterialen die gewoonlijk worden gebruikt om CMOS-transistoren en -verbindingen te maken, vormen fundamentele uitdagingen bij het voortdurend verkleinen van hun functiegroottes en lijden aan toenemende "contactweerstand" daartussen, die beide leiden tot verslechterende prestaties en een stijgend energieverbruik. Op grafeen gebaseerde transistors en interconnects zijn een veelbelovende technologie op nanoschaal die mogelijk problemen van traditionele op silicium gebaseerde transistors en metalen interconnects zou kunnen aanpakken.

"Naast zijn atomair dunne en ongerepte oppervlakken, grafeen heeft een afstembare band gap, die kan worden aangepast door lithografische schetsen van patronen - smalle grafeenlinten kunnen halfgeleidend worden gemaakt, terwijl bredere linten van metaal zijn. Vandaar, aaneengesloten grafeenlinten kunnen worden voorzien van hetzelfde uitgangsmateriaal om zowel actieve als passieve apparaten op een naadloze manier te ontwerpen en lagere interface-/contactweerstanden, " legde Kaustav Banerjee uit, hoogleraar elektrische en computertechniek en directeur van het Nanoelectronics Research Lab aan de UCSB. Het onderzoeksteam van Banerjee omvat ook UCSB-onderzoekers Jiahao Kang, Deblina Sarkar en Yasin Khatami. Hun werk is onlangs gepubliceerd in het tijdschrift Technische Natuurkunde Brieven .

"Nauwkeurige evaluatie van elektrisch transport door de verschillende op grafeen nanoribbon gebaseerde apparaten en interconnects en over hun interfaces was de sleutel tot ons succesvolle circuitontwerp en -optimalisatie, " legde Jiahao Kang uit, een promovendus in de groep van Banerjee en een co-auteur van de studie. De groep van Banerjee was een pionier in een methodologie met behulp van de Non-Equilibrium Green's Function (NEGF)-techniek om de prestaties van dergelijke complexe circuitschema's met veel heterojuncties te evalueren. Deze methodologie werd gebruikt bij het ontwerpen van een "volledig grafeen" logisch circuit dat in deze studie wordt gerapporteerd.

"Dit werk heeft een oplossing aangetoond voor het ernstige contactweerstandsprobleem dat wordt aangetroffen in conventionele halfgeleidertechnologie door een innovatief idee te bieden voor het gebruik van een volledig grafeen-apparaat-interconnect-schema. Dit zal het IC-fabricageproces van op grafeen gebaseerde nano-elektronische apparaten aanzienlijk vereenvoudigen." merkte Philip Kim op, hoogleraar natuurkunde aan de Columbia University, en een gerenommeerde wetenschapper in de grafeenwereld.

Zoals gerapporteerd in hun onderzoek, de voorgestelde volledig grafeencircuits hebben 1,7x hogere ruismarges en 1-2 decennia lager statisch stroomverbruik bereikt ten opzichte van de huidige CMOS-technologie. Volgens Banerjee, met de voortdurende wereldwijde inspanningen om grafeen te modelleren en te dopen, dergelijke circuits kunnen in de nabije toekomst worden gerealiseerd.

"We hopen dat dit werk andere onderzoekers zal aanmoedigen en inspireren om in de nabije toekomst grafeen en voorbij-grafeen opkomende 2-dimensionale kristallen te onderzoeken voor het ontwerpen van dergelijke 'band-gap-engineered' circuits, ’ voegde Banerjee eraan toe.

Bio-ingenieurs zetten stap in de richting van een patch die een gebroken hart kan herstellen

Bio-ingenieurs zetten stap in de richting van een patch die een gebroken hart kan herstellen Onderzoekers stellen vast hoe sorptiematerialen koolstof vangen en afgeven

Onderzoekers stellen vast hoe sorptiematerialen koolstof vangen en afgeven Bekledingstests tonen aan dat vocht de Grenfell-vlammen mogelijk heeft versneld

Bekledingstests tonen aan dat vocht de Grenfell-vlammen mogelijk heeft versneld In stikstof ingebedde polycyclische verbinding met sterke anti-aromaticiteit en stabiliteit

In stikstof ingebedde polycyclische verbinding met sterke anti-aromaticiteit en stabiliteit Wetenschappers vinden een goedkopere manier om OLED-schermen te verlichten

Wetenschappers vinden een goedkopere manier om OLED-schermen te verlichten

Ziekenhuizen lopen vol in meest vervuilde hoofdstad van Europa

Ziekenhuizen lopen vol in meest vervuilde hoofdstad van Europa De analogiemethode toepassen om de voorspelling van sterke convectie te verbeteren

De analogiemethode toepassen om de voorspelling van sterke convectie te verbeteren Kennis van zware stormpatronen kan tornado-waarschuwingen verbeteren

Kennis van zware stormpatronen kan tornado-waarschuwingen verbeteren Hoe krijgen planten eiwitten?

Hoe krijgen planten eiwitten?  Wetenschappers stellen voor om de regels van de geschiedenis te veranderen om de ineenstorting van het milieu te voorkomen

Wetenschappers stellen voor om de regels van de geschiedenis te veranderen om de ineenstorting van het milieu te voorkomen

Hoofdlijnen

- Soorten organellen

- Waarom insecten zich kunnen ontwikkelen uit onbevruchte eicellen

- Wat zijn de vier stikstofhoudende bases van DNA?

- Bacteriële harpoengeweer van nanoformaat werkt als een boormachine

- 6 soorten vrij beweegbare gewrichten

- Belangrijke feiten over het koninkrijk Monera

- Een konijn ontleden

- Hoe weet je lichaam het verschil tussen dominante en recessieve genen?

- Thuis op het strand:Antelope krijgt nieuwe opgravingen in New Orleans

- Klein apparaatje grijpt meer zonne-energie om water sneller te desinfecteren

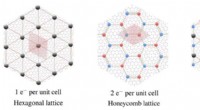

- Team vindt Wigner-kristal - niet Mott-isolator - in grafeen met magische hoek

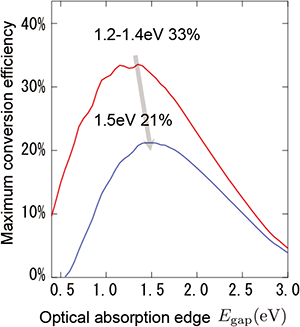

- Handleidingen voor het verhogen van de efficiëntie van organische zonnecellen

- Natuurkundigen lossen het mysterie op van verdwijnende deeltjes in grafeen

- Onderzoekers bouwen een transistor van een molecuul en een paar atomen

Ontwikkeling van een kweekset voor kunstmatige orchideeën

Ontwikkeling van een kweekset voor kunstmatige orchideeën Vergrendelde MOF's zijn de sleutel tot hoge porositeit

Vergrendelde MOF's zijn de sleutel tot hoge porositeit Wanneer sterrenstelsels botsen:Hubble toont zes prachtige fusies van sterrenstelsels

Wanneer sterrenstelsels botsen:Hubble toont zes prachtige fusies van sterrenstelsels Hoe schaarse medische benodigdheden te verdelen in een pandemie, en doe het eerlijk

Hoe schaarse medische benodigdheden te verdelen in een pandemie, en doe het eerlijk Hoe een UPC-nummer te verifiëren

Hoe een UPC-nummer te verifiëren  Uit onderzoek blijkt dat homo- en biseksuele jongeren vaker naar de kerk gaan als ze volwassen zijn

Uit onderzoek blijkt dat homo- en biseksuele jongeren vaker naar de kerk gaan als ze volwassen zijn Adsorberend materiaal ontwikkeld uit PET-flessen voor het verwijderen van antibiotica uit water

Adsorberend materiaal ontwikkeld uit PET-flessen voor het verwijderen van antibiotica uit water Volghalsbanden onthullen de geheimen van bavianen overvaltactieken

Volghalsbanden onthullen de geheimen van bavianen overvaltactieken

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com