Wetenschap

Nieuwe technieken maken op koolstof gebaseerde geïntegreerde schakelingen praktischer

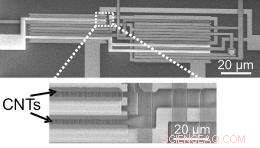

Een elektronenmicroscoopbeeld dat koolstofnanobuistransistors (CNT's) toont die zijn gerangschikt in een geïntegreerd logisch circuit.

(PhysOrg.com) -- Stanford-ingenieurs hebben volgens hen een chip gebouwd met de meest geavanceerde computer- en opslagelementen gemaakt van koolstofnanobuisjes tot nu toe door een manier te bedenken om de hardnekkige complicatie van nanobuisjes die kortsluiting veroorzaken uit te roeien.

nanobuisjes, die lijken op microscopisch kleine rietjes van opgerold kippengaas, worden algemeen beschouwd als de potentiële volgende generatie materialen voor het mogelijk maken van verbeterde snelheid en energie-efficiëntie van computerchips.

De onderzoekers presenteerden hun resultaten vandaag op de International Electron Devices Meeting (IEDM) in Baltimore, samen met een andere vooruitgang in het gebruik van nanobuisjes om meerlagige, driedimensionale schakelingen.

"Dit oeuvre illustreert dat koolstofnanobuis-transistortechnologie voorbij het rijk van wetenschappelijke ontdekkingen is gegaan en naar technisch onderzoek is gegaan, " zei H.-S. Philip Wong, een professor in elektrotechniek aan Stanford en een co-auteur van het artikel. "We zijn nu in staat om apparaten te bouwen en circuits te bouwen op waferschaal, in tegenstelling tot eerdere 'one-of-a-kind'-type demonstraties. Apparaten bevinden zich in een circuitomgeving die relevant is voor zowel de huidige als de toekomstige systeembehoeften."

Het handjevol nanobuistransistors in de circuits die het team heeft gefabriceerd, kan niet worden vergeleken met de honderden miljoenen transistors op een commerciële microprocessor of geheugenchip. maar hun regeling, de manier waarop ze zijn gemaakt en hun eigenschappen zijn veel dichter bij commerciële kwaliteit dan alle nanobuis-apparaten die eerder zijn gemaakt, zei Subhasish Mitra, een assistent-professor informatica en elektrotechniek aan Stanford.

De transistors zijn gegroepeerd in dezelfde "cascadering" sequenties die nodig zijn om computationele logica en geheugen te produceren, en het proces dat wordt gebruikt om ze te maken is compatibel met de industriële VLSI-productiestandaard (zeer grootschalige integratie).

"We zijn erg blij met de snelle vooruitgang die is geboekt door de professoren Wong en Mitra en hun onderzoeksteams bij het ontwikkelen van deze technologieën om belemmeringen voor verdere integratie van complexe op koolstof gebaseerde elektronische circuits te helpen overwinnen, wat zal leiden tot meer bruikbare producten voor toekomstige generaties, " zei Betsy Weitzman, executive vice president en directeur van het Focus Center Research Program van de Semiconductor Research Corporation, die hielpen bij het financieren van het onderzoek, samen met de National Science Foundation.

De chips maken gebruik van drie geavanceerde technieken die in Stanford zijn uitgevonden om endemische problemen in verband met nanobuisjes te overwinnen. Een, uitgevonden in 2007, laat transistoren werken, ongeacht of de component nanobuisjes perfect recht liggen. Een ander, uitgevonden in 2008, maakt fabricage op VLSI-schaal van nanobuistransistoren op een chip mogelijk. Degene die vandaag werd aangekondigd op de IEDM, is een proces voor het betrouwbaar verwijderen van nanobuisjes die altijd elektrische stroom geleiden, zelfs als dat niet de bedoeling is. Dergelijke lastige "metalen" nanobuisjes kunnen transistoren kortsluiten als ze niet worden verwijderd. De moeilijkheid waarmee onderzoekers te maken hebben gehad, is het vinden van manieren om alle lastige nanobuisjes te verwijderen, zonder enig ander deel van een circuit te beschadigen, inclusief de nanobuisjes die zich goed gedragen.

De nieuwe techniek, die de onderzoekers VLSI-compatibele Metallic Nanotube Removal (VMR) noemen, bouwt voort op een idee dat voor het eerst werd voorgesteld door Paul Collins en collega's van IBM in 2001. Dat idee was om de nanobuisjes op te breken door ze bloot te stellen aan hoge stroom. Het Stanford-team heeft het idee nu praktisch gemaakt op VLSI-schaal door een raster van elektroden te creëren die de ongewenste nanobuisjes wegzappen. Datzelfde elektroderooster kan vervolgens worden geëtst om elk circuitontwerp te produceren, inclusief degenen die gebruik maken van de hierboven genoemde door Stanford ontwikkelde technieken.

De hoofdauteur van de VMR-paper gepresenteerd op IEDM is elektrotechniek Stanford-student Nishant Patil. Andere auteurs zijn onder meer afgestudeerde elektrotechniekstudenten Albert Lin, Jie Zhang en Hai Wei, en student Kyle Anderson.

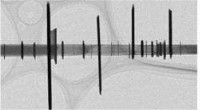

3D-nanobuiscircuits

Vijf leden van het team (Wei, Patil, Lin, Wong en Mitra) volgden het VMR-papier bij IEDM onmiddellijk op met een andere presentatie waarin de eerste meerlagige koolstofnanobuisjes driedimensionaal geïntegreerde schakeling werden beschreven.

Zoals parkeergarages met meerdere verdiepingen, driedimensionale circuits maken het mogelijk om meer eenheden in te pakken - in dit geval transistors - in een besloten ruimte. op fiches, de derde dimensie kan ook de lengtes van sommige onderling verbonden draden verminderen, het verminderen van de energie die nodig is voor gegevensoverdracht. Terwijl ingenieurs recentelijk vooruitgang hebben geboekt bij het bouwen van driedimensionale circuits door het stapelen en verbinden van lagen gemaakt met conventionele materialen, het werk van Stanford laat zien dat het kan met nanobuisjes op een manier die vanaf het begin is geïntegreerd als een 3D-ontwerp, wat een hogere dichtheid van verbindingen tussen lagen oplevert.

Aangeven dat vooruitgang mogelijk is met nanobuisjes, de Stanford-onderzoekers waren in staat om een prototype van een drielaagse chip te maken met tientallen nanobuistransistors die in werkende logische poorten waren verbonden door middel van nanobuisjes en metalen bedrading. Wat maakte de prestatie mogelijk, Mitra zei, was het gebruik van een relatief lage temperatuur proces dat de onderzoekers vorig jaar ontwikkelden, waarbij nanobuisjes van een kwartswafel op een siliciumchip worden overgebracht.

Een resterende uitdaging is het vergroten van het aantal nanobuisjes dat goed van een patroon kan worden voorzien op een bepaald gebied van een chip, om de miljoenen transistors te maken die moderne ontwerpen nodig hebben. Dat is geen hindernis die onderzoekers verwachten te laten liggen.

Beide projecten werden ondersteund door het Focus Center Research Program en de National Science Foundation's Directorate for Computer and Information Science and Engineering (CISE).

"NSF en in het bijzonder CISE, is zeer geïnteresseerd in het verkennen van opwindende nieuwe wegen om voortdurende verbeteringen van de hardwareprestaties te verkrijgen buiten de grenzen van de wet van Moore, " zei Sampath Kannan, een CISE-divisiedirecteur bij de National Science Foundation.

"Het team onder leiding van professoren Mitra en Wong, ondersteund door verschillende subsidies van CISE, is baanbrekend onderzoek langs een van deze wegen. Hun nieuwe resultaten op VLSI-schaaltechniek om met metalen koolstofnanobuizen voor circuitontwerp om te gaan en hun experimentele demonstratie van imperfectie-immune VLSI-compatibele CNT-circuits brengen ons dichter bij het maken van geïntegreerde schakelingen met behulp van koolstofnanobuizen een praktische realiteit."

Aangeboden door Stanford University (nieuws:web)

Detectie van antilichamen met gloeiende eiwitten, draad en een smartphone

Detectie van antilichamen met gloeiende eiwitten, draad en een smartphone Het verschil tussen atomen, ionen, moleculen en verbindingen

Het verschil tussen atomen, ionen, moleculen en verbindingen  Wetenschappers verbeteren de fietsprestaties van op Al gebaseerde batterijen met kathode met hoge oppervlaktedichtheid

Wetenschappers verbeteren de fietsprestaties van op Al gebaseerde batterijen met kathode met hoge oppervlaktedichtheid Nieuwe natuurwetten helpen mensen en robots de wrijving van aanraking te begrijpen

Nieuwe natuurwetten helpen mensen en robots de wrijving van aanraking te begrijpen Elektrochemische reductie van kooldioxide tot ethanol

Elektrochemische reductie van kooldioxide tot ethanol

Hoofdlijnen

- Hoe u uw hersenen kunt stimuleren

- Wat is osmotische lyse?

- Snellere Salmonella-test verhoogt voedselveiligheid voor mens en dier

- Scented Cleaning Products: The New Smoking?

- Het combineren van cassavemeel in het brooddeeg kan in de toekomst de toegang tot voedsel verzekeren

- Knoestige problemen in DNA

- Waarom wordt natrium gebruikt bij DNA-extractie?

- Geboren onder een ongunstige maan, babyvissen vertragen nederzetting op koraalriffen

- Welke drie dingen helpen bloed door aderen te duwen?

- Wetenschappers kweken zee-egelvormige structuren

- Door het transport van elektronen en ionen te beperken, wetenschappers laten zien dat ze materiaaleigenschappen kunnen veranderen

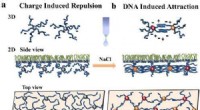

- DNA-gekoppelde nanodeeltjes vormen verwisselbare dunne films op een vloeibaar oppervlak

- Nieuw materiaal maakt ultradunne zonnecellen mogelijk

- Halfgeleider shish kabob nanostructuren combineren eigenschappen van verschillende dimensies

Onderzoekers rapporteren observatie van polaire skyrmionen bij kamertemperatuur

Onderzoekers rapporteren observatie van polaire skyrmionen bij kamertemperatuur Hoe een cumulatief numeriek gemiddelde te berekenen

Hoe een cumulatief numeriek gemiddelde te berekenen Cyprus worstelt met afvalbeheer nu het aantal toeristen stijgt

Cyprus worstelt met afvalbeheer nu het aantal toeristen stijgt Er is een tweede enorme plastic vuilnisbelt in de Stille Oceaan

Er is een tweede enorme plastic vuilnisbelt in de Stille Oceaan  Slecht nieuws brengen? Draai er niet omheen

Slecht nieuws brengen? Draai er niet omheen Studie bepaalt fundamentele parameters van de chemisch eigenaardige ster HD 108662

Studie bepaalt fundamentele parameters van de chemisch eigenaardige ster HD 108662 Matrices op een TI-84 wissen

Matrices op een TI-84 wissen  Vintage film laat zien dat de Thwaites Glacier-ijsplaat sneller smelt dan eerder werd waargenomen

Vintage film laat zien dat de Thwaites Glacier-ijsplaat sneller smelt dan eerder werd waargenomen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com