Wetenschap

Nieuwe neuromorfische chip voor AI aan de rand, met een fractie van de energie en omvang van de hedendaagse computerplatforms

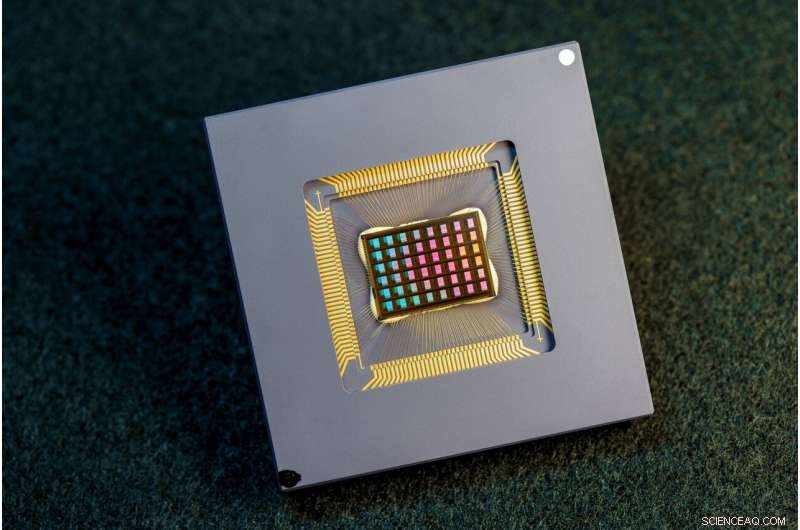

Een team van internationale onderzoekers heeft de NeuRRAM-chip ontworpen, vervaardigd en getest. Credit:David Baillot/Universiteit van Californië, San Diego

Een internationaal team van onderzoekers heeft een chip ontworpen en gebouwd die berekeningen rechtstreeks in het geheugen uitvoert en een breed scala aan AI-toepassingen kan uitvoeren, en dat alles tegen een fractie van de energie die wordt verbruikt door computerplatforms voor algemene AI-computing.

De neuromorfische chip van NeuRRAM brengt AI een stap dichter bij het draaien op een breed scala aan edge-apparaten, losgekoppeld van de cloud, waar ze overal en altijd geavanceerde cognitieve taken kunnen uitvoeren zonder afhankelijk te zijn van een netwerkverbinding met een gecentraliseerde server. Toepassingen zijn er in alle uithoeken van de wereld en in elk facet van ons leven, en variëren van slimme horloges tot VR-headsets, slimme oordopjes, slimme sensoren in fabrieken en rovers voor verkenning van de ruimte.

De NeuRRAM-chip is niet alleen twee keer zo energiezuinig als de state-of-the-art 'compute-in-memory'-chips, een innovatieve klasse hybride chips die berekeningen in het geheugen uitvoert, hij levert ook resultaten die net zo nauwkeurig zijn als conventionele digitale chips. Conventionele AI-platforms zijn veel omvangrijker en zijn doorgaans beperkt tot het gebruik van grote dataservers die in de cloud werken.

Bovendien is de NeuRRAM-chip zeer veelzijdig en ondersteunt hij veel verschillende neurale netwerkmodellen en architecturen. Hierdoor kan de chip voor veel verschillende toepassingen worden gebruikt, waaronder beeldherkenning en -reconstructie, evenals spraakherkenning.

"De conventionele wijsheid is dat de hogere efficiëntie van compute-in-memory ten koste gaat van veelzijdigheid, maar onze NeuRRAM-chip verkrijgt efficiëntie zonder in te boeten aan veelzijdigheid", zegt Weier Wan, de eerste corresponderende auteur van het artikel en een recente Ph.D. afgestudeerd aan Stanford University, die aan de chip werkte tijdens zijn studie aan UC San Diego, waar hij mede werd geadviseerd door Gert Cauwenberghs in de afdeling Bioengineering.

Het onderzoeksteam, mede geleid door bio-ingenieurs van de University of California San Diego, presenteert hun resultaten in het nummer van Nature van 17 augustus. .

Momenteel is AI-computing zowel energieverslindend als rekenkundig duur. Bij de meeste AI-toepassingen op edge-apparaten worden gegevens van de apparaten naar de cloud verplaatst, waar de AI deze verwerkt en analyseert. Vervolgens worden de resultaten terug naar het apparaat verplaatst. Dat komt omdat de meeste edge-apparaten op batterijen werken en als gevolg daarvan slechts een beperkte hoeveelheid stroom hebben die aan computers kan worden besteed.

Door het stroomverbruik dat nodig is voor AI-inferentie aan de edge te verminderen, kan deze NeuRRAM-chip leiden tot robuustere, slimmere en toegankelijkere edge-apparaten en slimmere productie. Het kan ook leiden tot betere gegevensprivacy, aangezien de overdracht van gegevens van apparaten naar de cloud grotere beveiligingsrisico's met zich meebrengt.

Op AI-chips is het verplaatsen van gegevens van geheugen naar rekeneenheden een groot knelpunt.

"Het is het equivalent van acht uur woon-werkverkeer voor een werkdag van twee uur," zei Wan.

Om dit probleem met gegevensoverdracht op te lossen, gebruikten onderzoekers wat bekend staat als resistief willekeurig toegankelijk geheugen, een type niet-vluchtig geheugen dat berekeningen rechtstreeks in het geheugen mogelijk maakt in plaats van in afzonderlijke rekeneenheden. RRAM en andere opkomende geheugentechnologieën die worden gebruikt als synaps-arrays voor neuromorfisch computergebruik, werden ontwikkeld in het laboratorium van Philip Wong, Wan's adviseur aan Stanford en een belangrijke bijdrage aan dit werk. Berekening met RRAM-chips is niet per se nieuw, maar leidt over het algemeen tot een afname van de nauwkeurigheid van de berekeningen die op de chip worden uitgevoerd en tot een gebrek aan flexibiliteit in de architectuur van de chip.

"Compute-in-memory is een gangbare praktijk in neuromorfische engineering sinds het meer dan 30 jaar geleden werd geïntroduceerd," zei Cauwenberghs. "Wat nieuw is aan NeuRRAM is dat de extreme efficiëntie nu samengaat met een grote flexibiliteit voor diverse AI-toepassingen met bijna geen verlies aan nauwkeurigheid ten opzichte van standaard digitale algemene rekenplatforms."

Een zorgvuldig ontworpen methodologie was de sleutel tot het werk met meerdere niveaus van "co-optimalisatie" over de abstractielagen van hardware en software, van het ontwerp van de chip tot de configuratie om verschillende AI-taken uit te voeren. Bovendien zorgde het team ervoor dat rekening werd gehouden met verschillende beperkingen die variëren van de fysica van geheugenapparaten tot circuits en netwerkarchitectuur.

"Deze chip biedt ons nu een platform om deze problemen over de hele stapel aan te pakken, van apparaten en circuits tot algoritmen", zegt Siddharth Joshi, een assistent-professor informatica en engineering aan de Universiteit van Notre Dame, die aan het project begon te werken als een doctoraat student en postdoctoraal onderzoeker in Cauwenberghs lab aan UC San Diego.

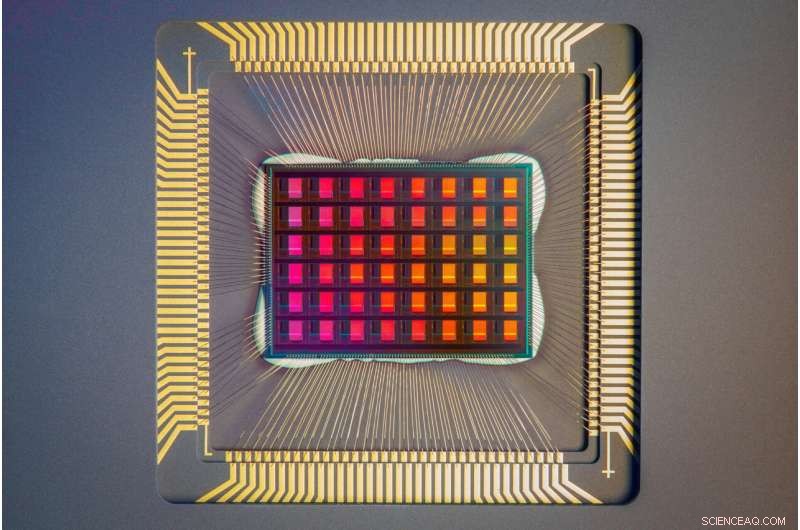

Een close-up van de NeuRRAM-chip. Credit:David Baillot/Universiteit van Californië, San Diego

Chipprestaties

Onderzoekers hebben de energie-efficiëntie van de chip gemeten met een maatregel die bekend staat als energievertragingsproduct of EDP. EDP combineert zowel de hoeveelheid energie die voor elke bewerking wordt verbruikt als de tijd die nodig is om de bewerking te voltooien. Door deze maatregel behaalt de NeuRRAM-chip een 1,6 tot 2,3 keer lagere EDP (lager is beter) en een 7 tot 13 keer hogere rekendichtheid dan state-of-the-art chips.

Onderzoekers voerden verschillende AI-taken uit op de chip. Het bereikte 99% nauwkeurigheid bij een handgeschreven cijferherkenningstaak; 85,7% op een taak voor beeldclassificatie; en 84,7% op een Google spraakopdrachtherkenningstaak. Bovendien behaalde de chip ook een vermindering van 70% in beeldreconstructiefouten bij een beeldhersteltaak. Deze resultaten zijn vergelijkbaar met bestaande digitale chips die berekeningen uitvoeren met dezelfde bitprecisie, maar met drastische besparingen in energie.

Researchers point out that one key contribution of the paper is that all the results featured are obtained directly on the hardware. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

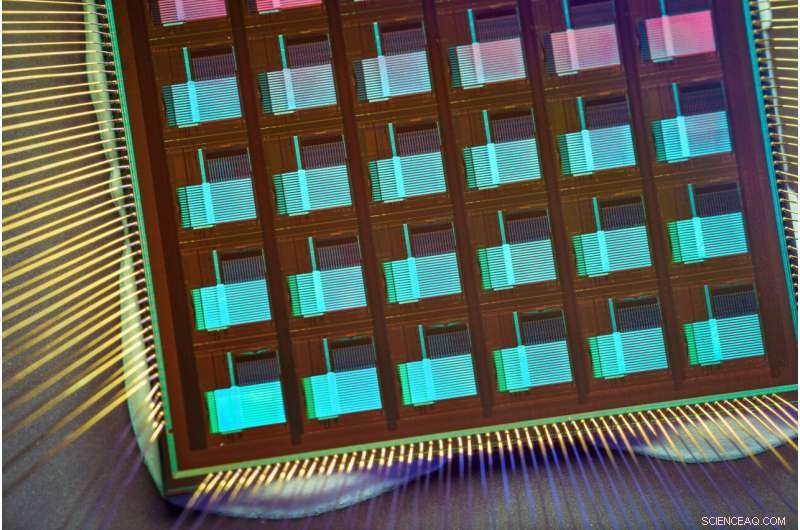

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. + Verder verkennen

A four-megabit nvCIM macro for edge AI devices

Hoe weet ik of iets polair of niet-polair is

Hoe weet ik of iets polair of niet-polair is  Wetenschappers bevestigen verschillende regio's in het populaire oplosmiddel voor het opvangen en synthetiseren van koolstof

Wetenschappers bevestigen verschillende regio's in het populaire oplosmiddel voor het opvangen en synthetiseren van koolstof Zuurstof geven aan de kwestie van luchtkwaliteit

Zuurstof geven aan de kwestie van luchtkwaliteit Belangrijkste soorten alcohol

Belangrijkste soorten alcohol Birnessietstudie biedt inzichten voor elektrochemie, energie opslag

Birnessietstudie biedt inzichten voor elektrochemie, energie opslag

Koolteerkit belangrijke bron van PAK-verontreiniging in zijrivieren van de Grote Meren

Koolteerkit belangrijke bron van PAK-verontreiniging in zijrivieren van de Grote Meren Kunnen we regen drinken? Onderzoekers nemen een kijkje

Kunnen we regen drinken? Onderzoekers nemen een kijkje Science Fair Project on Clouds

Science Fair Project on Clouds De meeste Amerikanen willen dat de regering klimaatverandering tegengaat, sommigen bereid om een hoog bedrag te betalen

De meeste Amerikanen willen dat de regering klimaatverandering tegengaat, sommigen bereid om een hoog bedrag te betalen Vergroening op hoge breedtegraden kan de uitbreiding van woestijnen op gemiddelde breedtegraden remmen

Vergroening op hoge breedtegraden kan de uitbreiding van woestijnen op gemiddelde breedtegraden remmen

Hoofdlijnen

- Hoe lepra werkt

- Wetenschappers volgen haaien die DNA-fragmenten uit de zee plukken

- Hoe zijn bacteriën en plantencellen gelijk?

- Hoe Tiny Robots je gezondheid kunnen verbeteren vanuit het lichaam

- Sommige microben wachten totdat hun gastheren hen onbewust het signaal geven om zich te vermenigvuldigen en ze te doden

- Afrikaanse slaapziekte:hoe de ziekteverwekker tseetseevliegen koloniseert

- Ouderleeftijd kan een belangrijke factor zijn om volbloedpaarden als eerste voorbij de post te helpen

- Geheugenhack:doe wat aerobics vier uur na de les

- 10 tips van gelukkige mensen

- Musks laatste reden om Twitter-deal te laten vallen:klokkenluiderbetaling

- AT&T zegt dat de HBO Max-streamingservice in mei wordt gelanceerd voor $ 15

- Met fietsen, doorvoer, Uber onthult visie op stadsvervoer

- General Electric daalde van Dow Jones-aandelenindex

- Herschikken van de lagen in zonnecelmodules kan de efficiëntie helpen verbeteren

Nieuwe met lucht gevulde vezelbundel kan endoscopen kleiner maken

Nieuwe met lucht gevulde vezelbundel kan endoscopen kleiner maken Door mist snijden met laserfocus

Door mist snijden met laserfocus Wat voor soort Biome is Redwood National Park In?

Wat voor soort Biome is Redwood National Park In?  Hoe HP naar Amps & Volts

Hoe HP naar Amps & Volts De ademende Himalaya:Grote bergen groeien in een cyclus van stijgen en dalen

De ademende Himalaya:Grote bergen groeien in een cyclus van stijgen en dalen Kristallen snel maken

Kristallen snel maken Nanotechnologie gebruiken om kankerbehandeling te verbeteren

Nanotechnologie gebruiken om kankerbehandeling te verbeteren Robots die met 3D-printers zijn gemaakt, kunnen voor degenen in gouden jaren zorgen

Robots die met 3D-printers zijn gemaakt, kunnen voor degenen in gouden jaren zorgen

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com