Wetenschap

Lithografie een curve geven:onderzoek introduceert de co-optimalisatiemethode voor maskerwafels

In het hart van de voortschrijdende halfgeleiderchiptechnologie ligt een cruciale uitdaging:het creëren van kleinere, efficiëntere elektronische componenten. Deze uitdaging is vooral duidelijk op het gebied van lithografie, het proces dat wordt gebruikt om ingewikkelde patronen te creëren op halfgeleidermaterialen (wafers genoemd) voor de productie van chips.

Lithografie maakt gebruik van een soort sjabloon, een fotomasker genoemd – of gewoon een masker – voor het creëren van patronen op halfgeleiderwafels. De industrie is altijd op zoek naar methoden die de resolutie en maakbaarheid van zowel maskers als wafers verbeteren, waardoor snellere chips worden geproduceerd met een hogere opbrengst aan goed functionerende chips.

Computationele lithografietechnieken die de resolutie en patroongetrouwheid verbeteren, zoals optische nabijheidscorrectie (OPC), hebben aanzienlijke vooruitgang geboekt bij het aanpakken van deze uitdagingen door de individuele maskerpatronen aan te passen om zowel het masker- als het waferprinten te verbeteren.

Inverse lithografietechnologie (ILT) – een wiskundig rigoureuze inverse benadering die de maskervormen bepaalt die de gewenste resultaten op de wafer zullen opleveren – wordt gezien als een veelbelovende oplossing voor veel van de uitdagingen van lithografie voor geavanceerde chips. Sinds de introductie ervan, meer dan tien jaar geleden, zijn er talloze onderzoeken geweest die aantonen dat vooral kromlijnige ILT-maskervormen de beste waferresultaten opleveren.

Tot voor kort hebben de looptijden die met deze rekentechniek gepaard gaan, de praktische toepassing ervan echter beperkt tot kritische "hotspots" op chips. In 2019 werd een geheel nieuw, speciaal gebouwd systeem voorgesteld, inclusief een unieke GPU-versnelde aanpak die een enkel gigantisch GPU/CPU-paar emuleert dat in één keer een volledige ILT-oplossing met volledige chip kan berekenen. Deze nieuwe aanpak, systematisch ontworpen voor ILT- en GPU-versnelling, maakte ILT met volledige chip tot een praktische realiteit in productie.

Deze benadering was echter gebaseerd op maskerschrijven met meerdere bundels, een belangrijke nieuwe ontwikkeling op het gebied van maskerschrijven die op pixels is gebaseerd en dus vorm-agnostisch is in termen van schrijftijd. De vraag die overbleef was of de voordelen van kromlijnige ILT met volledige chip zouden kunnen worden uitgebreid tot de VSB-maskerschrijvers (variable Shaped Beam) die rechtlijnige (en soms driehoekige) vormen schrijven in plaats van pixels, en die de meerderheid van de maskerschrijvers vormen. over de hele wereld vandaag.

Terwijl VSB-schrijvers snel grotere rechthoekige vormen creëren door één rechthoekig shot tegelijk te schrijven, kunnen complexe maskerpatronen een probleem zijn, omdat het schrijven van het grote aantal kleine rechthoeken dat nodig is om ze te maken te lang zou duren.

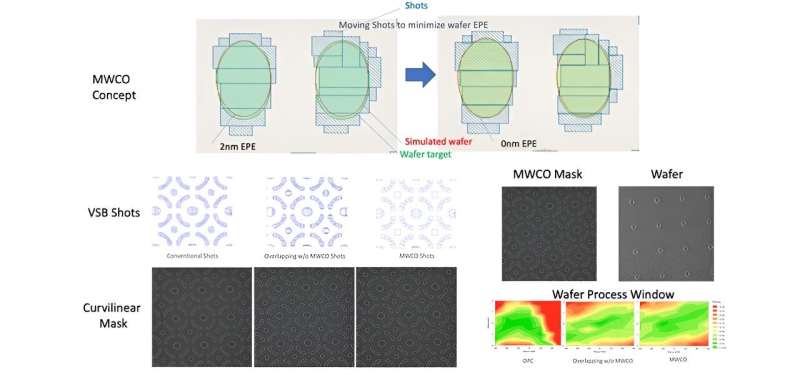

Rapporteren van hun werk in het Journal of Micro/Nanopatterning, Materials, and Metrology heeft het team van D2S, Inc. een methode uitgevonden genaamd mask wafer co-optimization (MWCO) met drie inzichten:de maskerschrijver en de waferscanner zijn beide laagdoorlaatfilters; overlappende opnamen, geleid door masker-/wafelsimulatie, kunnen kromlijnige vormen creëren met minder opnamen; door te richten op het wafelpatroon, in plaats van op het maskerpatroon, kan men veel eenvoudiger opnames maken om het juiste wafelpatroon af te drukken. Door gebruik te maken van deze dubbele simulatie wordt de waferprintkwaliteit iteratief geoptimaliseerd, terwijl de VSB-opnameranden worden gemanipuleerd om rechtlijnige doelmaskervormen te produceren waarvan bekend is dat ze beschrijfbaar zijn op een VSB-schrijver, met een bekend en acceptabel aantal opnames.

D2S en Micron Technology hebben aangetoond dat MWCO de wafervariatie met 3x kan verminderen en het waferprocesvenster met 2x kan verbeteren in vergelijking met Micron OPC, wat wijst op een substantiële verbetering in de precisie en betrouwbaarheid van het lithografieproces. De schrijftijd voor een volledig kromlijnig ILT-masker zou minder dan 12 uur bedragen, wat voldoet aan de productievereisten voor grote volumes.

Dit betekent dat alle halfgeleiderfabrikanten nu chips kunnen produceren die niet alleen kleiner zijn, maar ook hogere prestaties en een lager energieverbruik hebben, zelfs als ze geen toegang hebben tot een maskerschrijver met meerdere bundels.

Meer informatie: Linyong (Leo) Pang et al., Maak het onmogelijke mogelijk:gebruik straalmaskerschrijvers met variabele vorm en kromlijnige full-chip inverse lithografietechnologie voor 193i-contacten/via's met masker-wafer-co-optimalisatie, Journal of Micro/Nanopatterning, Materialen en metrologie (2024). DOI:10.1117/1.JMM.23.1.011207

Geleverd door SPIE

Nieuwe katalysator opent de deur naar het afvangen van kooldioxide bij de omzetting van steenkool in vloeibare brandstoffen

Nieuwe katalysator opent de deur naar het afvangen van kooldioxide bij de omzetting van steenkool in vloeibare brandstoffen Wat zijn de 4 atoommodellen?

Wat zijn de 4 atoommodellen?  Gerichte evolutie opent deur naar nieuwe antibiotica

Gerichte evolutie opent deur naar nieuwe antibiotica Nieuwe aardgaskatalysator zou schoon transport stimuleren

Nieuwe aardgaskatalysator zou schoon transport stimuleren Gelijktijdige emissie van orthogonale handigheid in circulaire polarisatie

Gelijktijdige emissie van orthogonale handigheid in circulaire polarisatie

Hoofdlijnen

- Supermensen creëren door middel van genmanipulatie en meer

- Procedures voor elektroforese van gel

- Nieuwe methode produceert verser en smakelijker koudgeperst Concord-druivensap

- NOAA rapporteert een aanhoudende daling van de overbevissing

- Gewone schimmel helpt het knokkelkoortsvirus te gedijen bij muggen

- Teams Advance maakt het bewerken van genen met chirurgische precisie mogelijk

- Mediterrane wijnmakerijen bevinden zich in een klimaathotspot. Klimatologen helpen hen zich aan te passen

- Analyse van het potentieel van AlphaFold bij het ontdekken van geneesmiddelen

- Elk levend wezen maakt deel uit van een ecosysteem. Hier is hoe ze werken

Rijkere intracellulaire opnames ontgrendelen

Rijkere intracellulaire opnames ontgrendelen Fusie van neutronensterren resulteert in magnetar met helderste kilonova ooit waargenomen

Fusie van neutronensterren resulteert in magnetar met helderste kilonova ooit waargenomen Kathodemateriaal gemaakt van organische moleculen verbetert de groene eigenschappen van oplaadbare batterijen

Kathodemateriaal gemaakt van organische moleculen verbetert de groene eigenschappen van oplaadbare batterijen Hoe Venetië, Italië de CO2-uitstoot van sociale woningbouw kan verminderen

Hoe Venetië, Italië de CO2-uitstoot van sociale woningbouw kan verminderen Gefuseerde beeldvorming onthult zesde-eeuws schrift verborgen in boekbinden

Gefuseerde beeldvorming onthult zesde-eeuws schrift verborgen in boekbinden Hoe we kritische grondstoffen in de katalyse kunnen vervangen, elektronica en fotonica

Hoe we kritische grondstoffen in de katalyse kunnen vervangen, elektronica en fotonica Zwaartekrachtgolfmissie geselecteerd, missie op planeetjacht gaat vooruit

Zwaartekrachtgolfmissie geselecteerd, missie op planeetjacht gaat vooruit Eind-Perm uitsterven, die de meeste aardse soorten heeft uitgeroeid, was ogenblikkelijk in geologische tijd

Eind-Perm uitsterven, die de meeste aardse soorten heeft uitgeroeid, was ogenblikkelijk in geologische tijd

- Elektronica

- Biologie

- Zonsverduistering

- Wiskunde

- French | Italian | Spanish | Portuguese | Swedish | German | Dutch | Danish | Norway |

-

Wetenschap © https://nl.scienceaq.com